MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

8-6 Freescale Semiconductor

If an attempt to force a non-correctable error (by asserting ECSM_EEGR[FRCNCI] or

ECSM_EEGR[FRC1NCI]) and ECSM_EEGR[ERRBIT] equals 64, then no data error will be generated.

NOTE

The only allowable values for the 2 control bit enables {FRCNCI, FR1NCI}

are {0,0}, {1,0} and {0,1}. The value {1,1} results in undefined behavior.

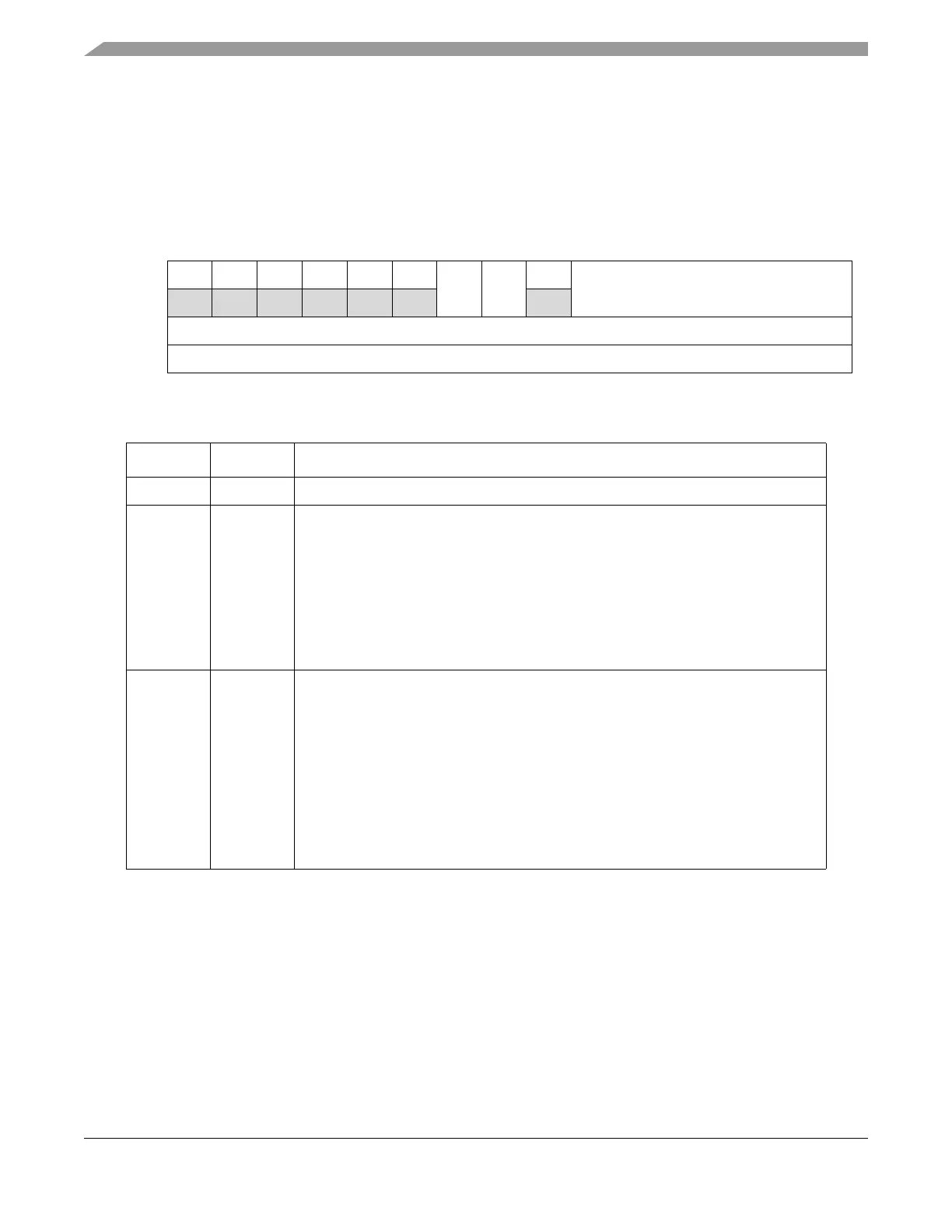

0123456789101112131415

R000000FRC

NCI

FR1

NCI

0 ERRBIT[0:6]

W

Reset0000000000000000

Reg Addr Base + 0x004A

Figure 8-3. ECC Error Generation (ECSM_EEGR) Register

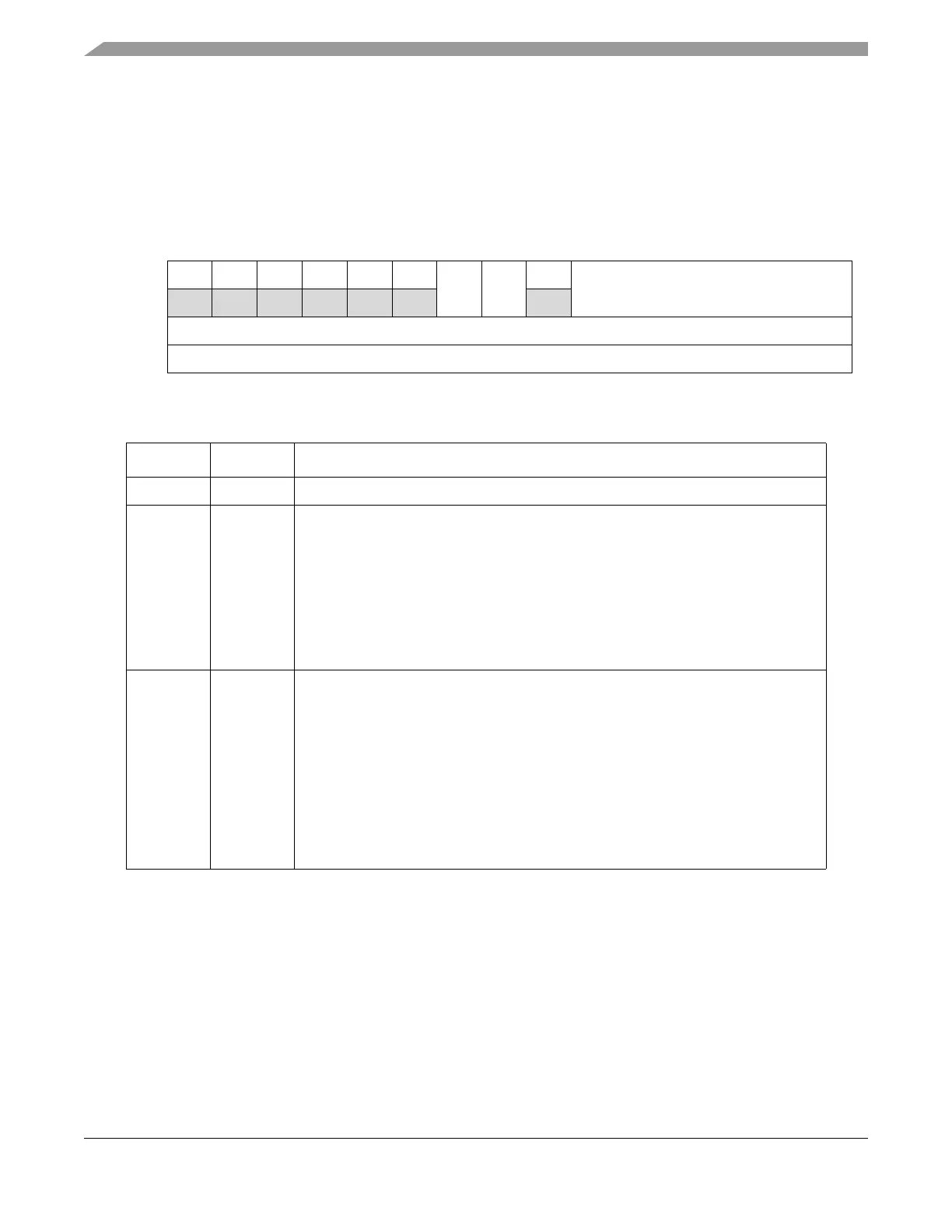

Table 8-5. ECSM_EEGR Field Definitions

Bits Name Description

0–5 — Reserved.

6 FRCNCI Force internal SRAM continuous noncorrectable data errors.

0 No internal SRAM continuous 2-bit data errors are generated.

1 2-bit data errors in the internal SRAM are continuously generated.

The assertion of this bit forces the internal SRAM controller to create 2-bit data errors,

as defined by the bit position specified in ERRBIT[0:6] and the overall odd parity bit,

continuously on every write operation.

The normal ECC generation takes place in the RAM controller, but then the polarity of

the bit position defined by ERRBIT and the overall odd parity bit are inverted to

introduce a 2-bit ECC error in the RAM.

7 FR1NCI Force internal SRAM one noncorrectable data errors.

0 No internal SRAM single 2-bit data errors are generated.

1 One 2-bit data error in the internal SRAM is generated.

The assertion of this bit forces the internal SRAM controller to create one 2-bit data

error, as defined by the bit position specified in ERRBIT[0:6] and the overall odd parity

bit, on the first write operation after this bit is set.

The normal ECC generation takes place in the internal SRAM controller, but then the

polarity of the bit position defined by ERRBIT and the overall odd parity bit are inverted

to introduce a 2-bit ECC error in the RAM.

After this bit has been enabled to generate a single 2-bit error, it must be cleared

before being set again to properly re-enable the error generation logic.

Loading...

Loading...