MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 8-5

which are loaded on each occurrence of an properly-enabled ECC event. If there is a pending ECC

interrupt and another properly-enabled ECC event occurs, the ECSM hardware automatically handles the

ECSM_ESR reporting, clearing the previous data and loading the new state and thus guaranteeing that

only a single flag is asserted.

To maintain the coherent software view of the reported event, the following sequence in the ECSM error

interrupt service routine is suggested:

1. Read the ECSM_ESR and save it.

2. Read and save all the address and attribute reporting registers.

3. Re-read the ECSM_ESR and verify the current contents matches the original contents. If the two

values are different, go back to step 1 and repeat.

4. When the values are identical, write a 1 to the asserted ECSM_ESR flag to negate the interrupt

request.

In the event that multiple status flags are signaled simultaneously, ECSM records the event with the RNCE

as highest priority, and then FNCE.

8.2.1.5 ECC Error Generation Register (ECSM_EEGR)

The ECSM_EEGR is a 16-bit control register used to force the generation of double-bit data errors in the

internal SRAM. This capability provides a mechanism to allow testing of the software service routines

associated with memory error logging.The intent is to generate errors during data write cycles, such that

subsequent reads of the corrupted address locations generate ECC events, double-bit noncorrectable errors

that are terminated with an error response.

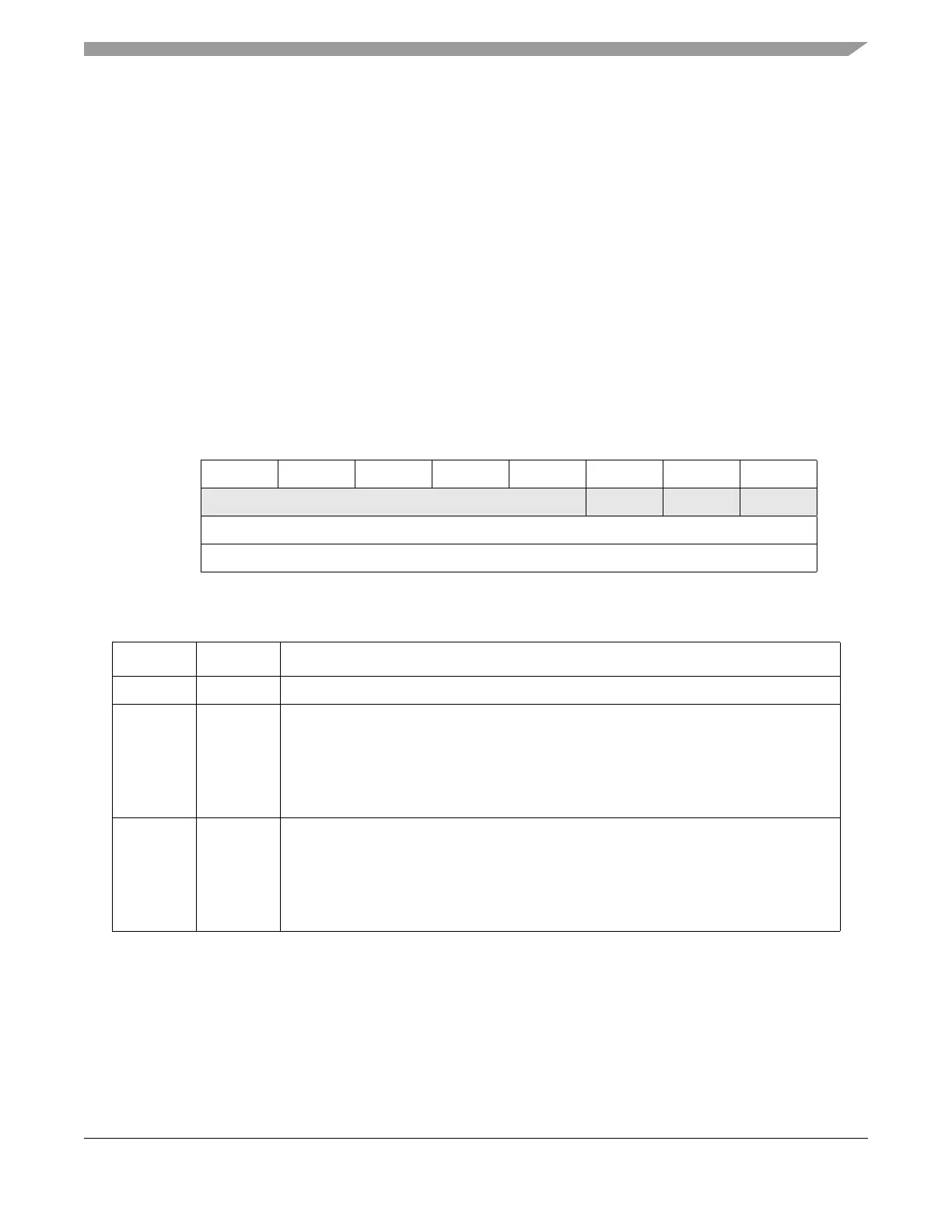

01234567

R000000RNCEFNCE

W w1c w1c

Reset00000000

Reg Addr Base + 0x0047

Figure 8-2. ECC Status Register (ECSM_ESR)

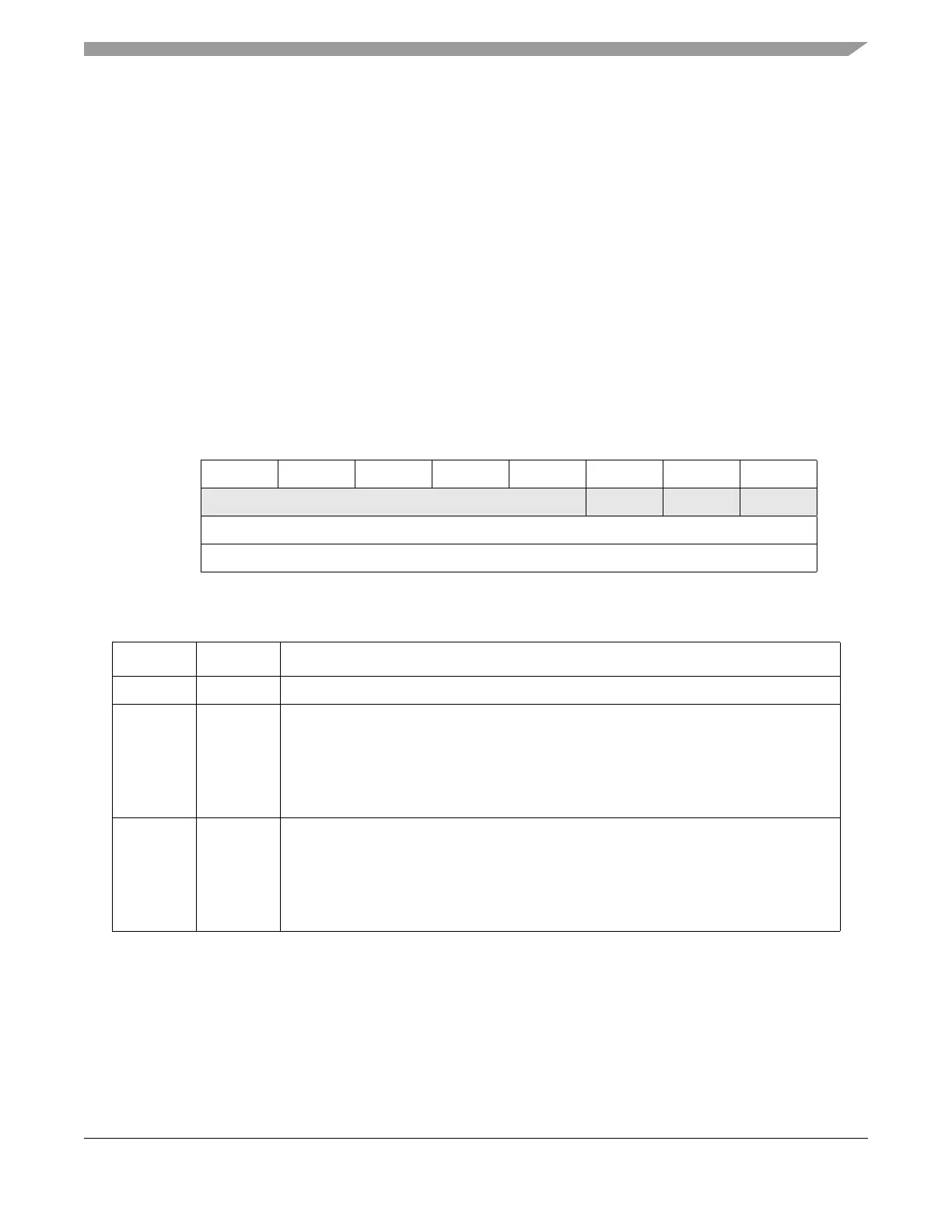

Table 8-4. ECSM_ESR Field Definitions

Bits Name Description

0–5 — Reserved.

6 RNCE RAM non-correctable error. The occurrence of a properly-enabled non-correctable RAM

error generates an ECSM ECC interrupt request. The faulting address, attributes and data

are also captured in the REAR, REMR, REAT and REDR registers. To clear this interrupt

flag, write a 1 to this bit. Writing a 0 has no effect.

0 No reportable non-correctable RAM error has been detected.

1 A reportable non-correctable RAM error has been detected.

7 FNCE Flash non-correctable error. The occurrence of a properly-enabled non-correctable flash

error generates an ECSM ECC interrupt request. The faulting address, attributes and data

are also captured in the FEAR, FEMR, FEAT and FEDR registers. To clear this interrupt

flag, write a 1 to this bit. Writing a 0 has no effect.

0 No reportable non-correctable flash error has been detected.

1 A reportable non-correctable flash error has been detected.

Loading...

Loading...