MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 20-9

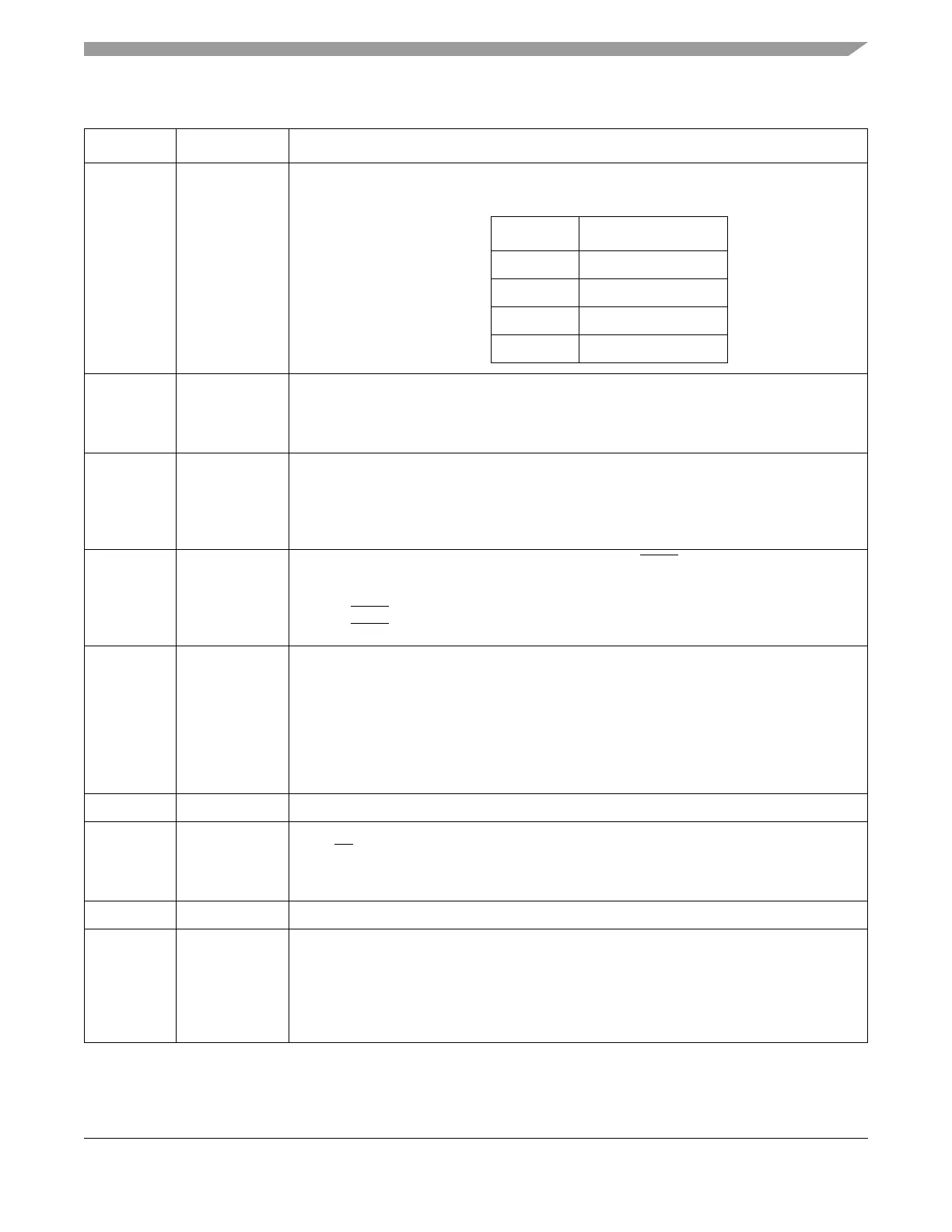

2–3 DCONF

[0:1]

DSPI configuration. Selects between the three different configurations of the DSPI. The table

below lists the DCONF values for the various configurations.

4 FRZ Freeze. Enables the DSPI transfers to be stopped on the next frame boundary when the

MPC5553/MPC5554 enters debug mode.

0 Do not halt serial transfers

1 Halt serial transfers

5 MTFE Modified timing format enable. Enables a modified transfer format to be used. See

Section 20.4.7.4, “Modified SPI/DSI Transfer Format (MTFE = 1, CPHA = 1),” for more

information.

0 Modified SPI transfer format disabled

1 Modified SPI transfer format enabled

6 PCSSE Peripheral chip select strobe enable. Enables the PCS5/PCSS

to operate as an PCS strobe

output signal. See Section 20.4.6.5, “Peripheral Chip Select Strobe Enable (PCSS),” for more

information.

0 PCS5/PCSS

is used as the Peripheral chip select 5 signal

1 PCS5/PCSS

is used as an active-low PCS strobe signal

7 ROOE Receive FIFO overflow overwrite enable. Enables an RX FIFO overflow condition to either

ignore the incoming serial data or to overwrite existing data. If the RX FIFO is full and new

data is received, the data from the transfer that generated the overflow is either ignored or

shifted in to the shift register. If the ROOE bit is asserted, the incoming data is shifted in to the

shift register. If the ROOE bit is negated, the incoming data is ignored. See Section 20.4.9.6,

“Receive FIFO Overflow Interrupt Request (RFOF),” for more information.

0 Incoming data is ignored

1 Incoming data is shifted in to the shift register

8–9 — Reserved, but implemented. These bits are writable, but have no effect.

10–15 PCSISn Peripheral chip select inactive state. Determines the inactive state of the PCSn signal.

PCS0/SS

must be configured as inactive high for slave mode operation.

0 The inactive state of PCSn is low

1 The inactive state of PCSn is high

16 — Reserved.

17 MDIS Module disable. Allows the clock to be stopped to the non-memory mapped logic in the DSPI

effectively putting the DSPI in a software controlled power-saving state. See Section 20.4.10,

“Power Saving Features for more information.” The reset value of the MDIS bit is

parameterized, with a default reset value of 0.

0 Enable DSPI clocks

1 Allow external logic to disable DSPI clocks

Table 20-3. DSPIx_MCR Field Descriptions (Continued)

Bits Name Description

DCONF Configuration

00 SPI

01 DSI

10 CSI

11 Reserved

Loading...

Loading...