MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

20-10 Freescale Semiconductor

18 DIS_TXF Disable transmit FIFO. Provides a mechanism to disable the TX FIFO. When the TX FIFO is

disabled, the transmit part of the DSPI operates as a simplified double-buffered SPI. See

Section 20.4.3.3, “FIFO Disable Operation for details.”

0 TX FIFO is enabled

1TX FIFO is disabled

19 DIS_RXF Disable receive FIFO. Provides a mechanism to disable the RX FIFO. When the RX FIFO is

disabled, the receive part of the DSPI operates as a simplified double-buffered SPI. See

Section 20.4.3.3, “FIFO Disable Operation for details.”

0 RX FIFO is enabled

1 RX FIFO is disabled

20 CLR_TXF Clear TX FIFO. Flushes the TX FIFO. Writing a 1 to CLR_TXF clears the TX FIFO counter.

The CLR_TXF bit is always read as zero.

0 Do not clear the TX FIFO counter

1 Clear the TX FIFO counter

21 CLR_RXF Clear RX FIFO. Flushes the RX FIFO. Writing a 1 to CLR_RXF clears the RX counter. The

CLR_RXF bit is always read as zero.

0 Do not clear the RX FIFO counter

1 Clear the RX FIFO counter

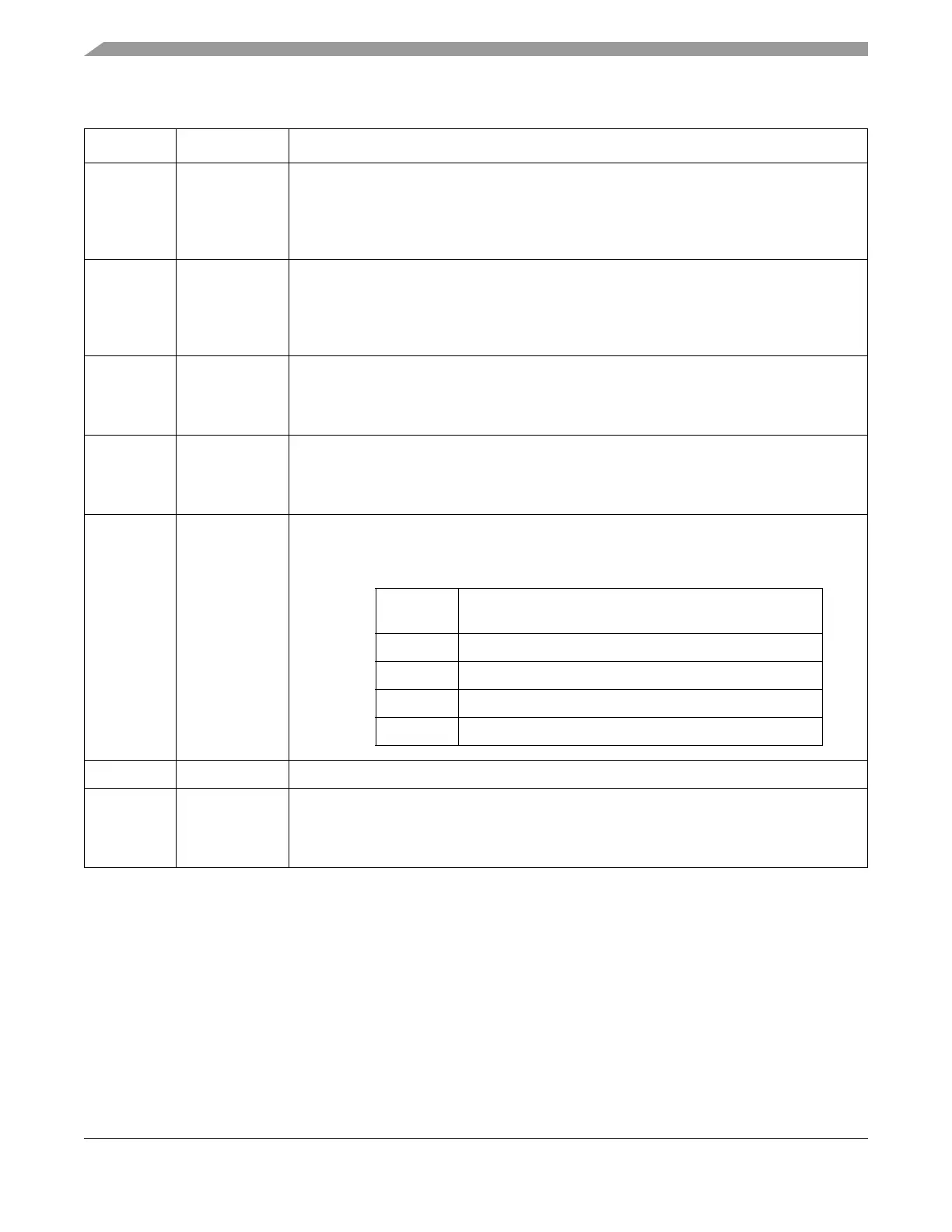

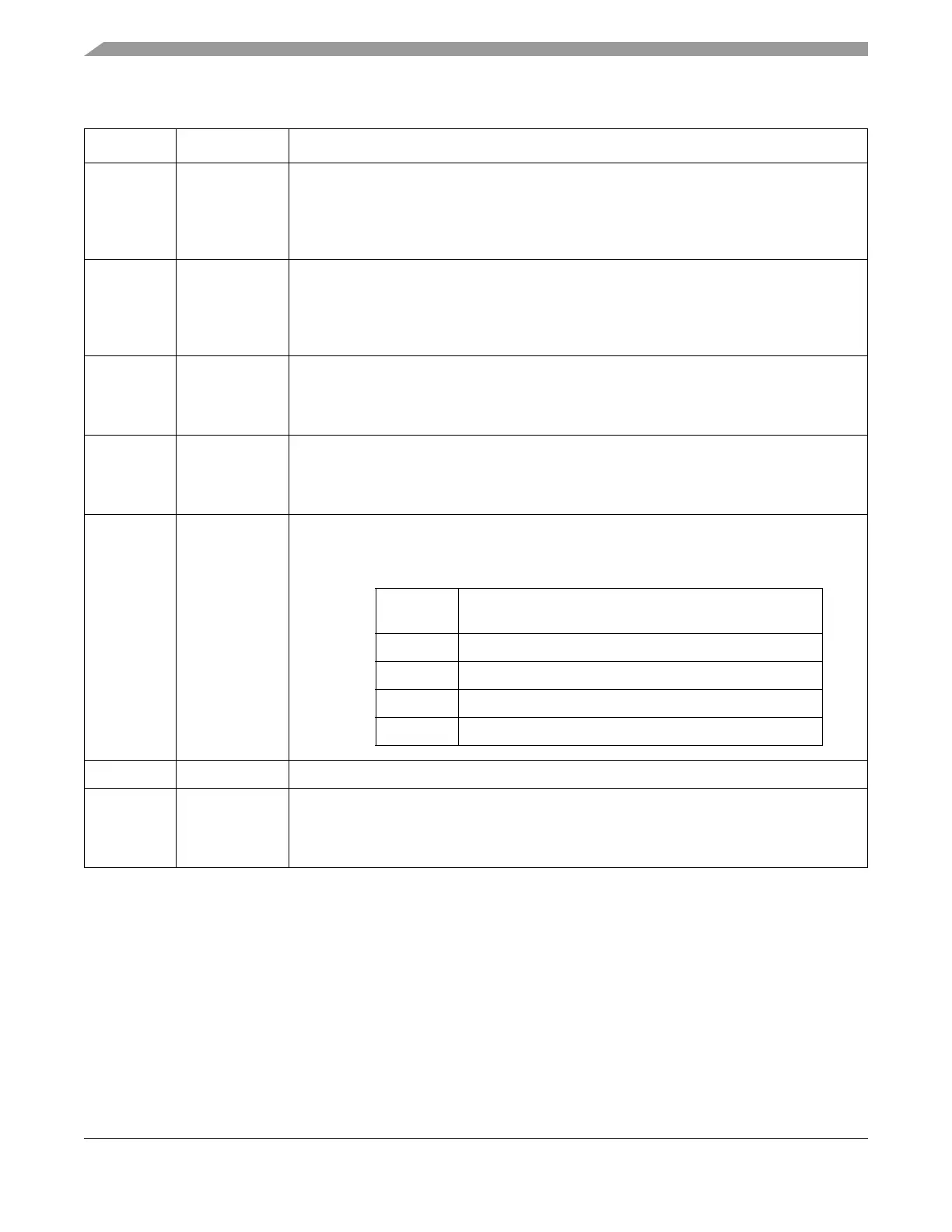

22–23 SMPL_PT

[0:1]

Sample point. Allows the host software to select when the DSPI master samples SIN in

modified transfer format. Figure 20-38 shows where the master can sample the SIN pin. The

table below lists the various delayed sample points.

24–30 — Reserved.

31 HALT Halt. Provides a mechanism for software to start and stop DSPI transfers. See Section 20.4.2,

“Start and Stop of DSPI Transfers,” for details on the operation of this bit.

0 Start transfers

1 Stop transfers

Table 20-3. DSPIx_MCR Field Descriptions (Continued)

Bits Name Description

SMPL_PT Number of system clock cycles between

odd-numbered edge of SCK and sampling of SIN.

00 0

01 1

10 2

11 Reserved

Loading...

Loading...