MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 20-7

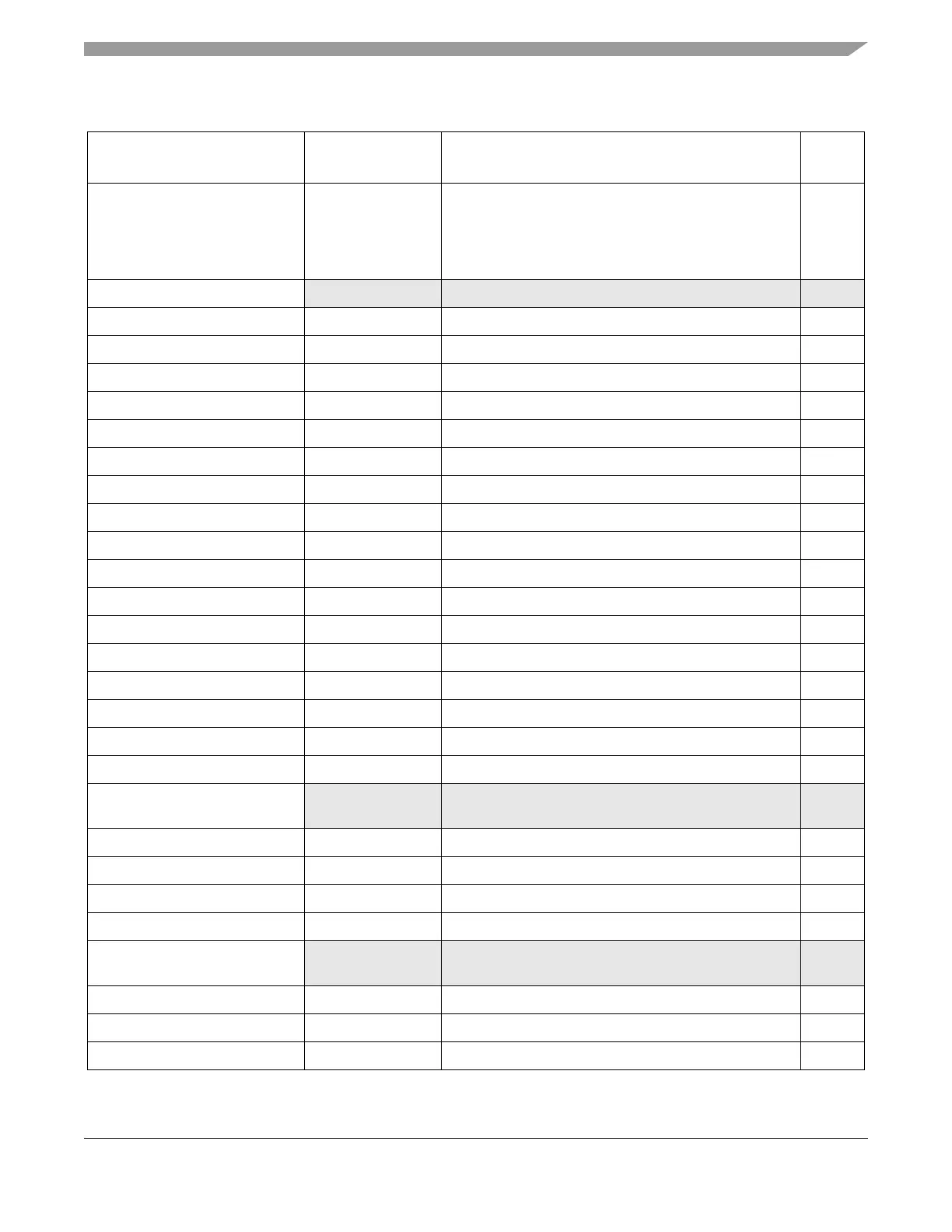

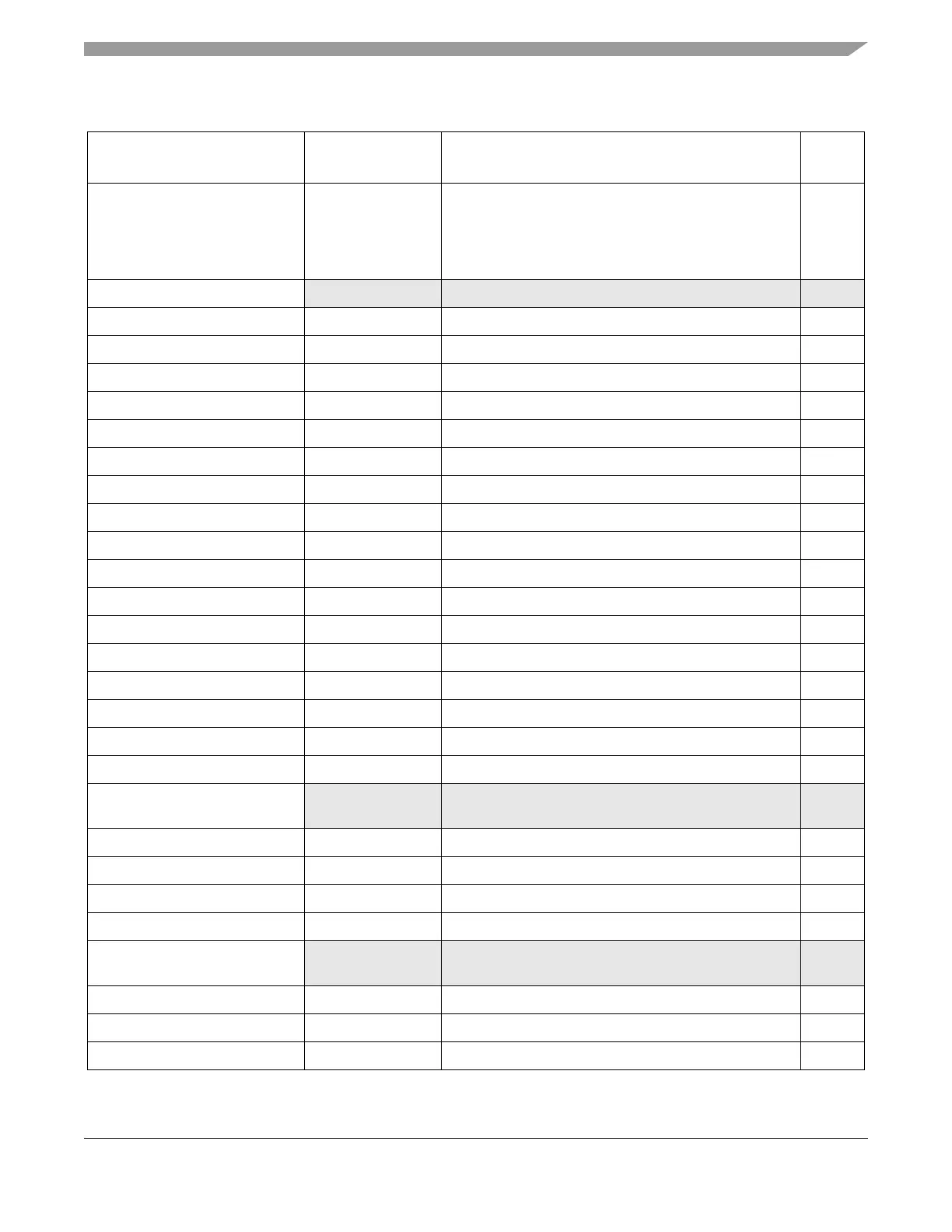

Table 20-2. DSPI Detailed Memory Map

Address Register Name Register Description

Size

(bits)

Base:

0xFFF9_0000 (DSPI A)

1

0xFFF9_4000 (DSPI B)

0xFFF9_8000 (DSPI C)

0xFFF9_C000 (DSPI D)

DSPIx_MCR DSPI module configuration register 32

Base + 0x0004

— Reserved —

Base + 0x0008 DSPIx_TCR DSPI transfer count register 32

Base + 0x000C DSPIx_CTAR0 DSPI clock and transfer attributes register 0 32

Base + 0x0010 DSPIx_CTAR1 DSPI clock and transfer attributes register 1 32

Base + 0x0014 DSPIx_CTAR2 DSPI clock and transfer attributes register 2 32

Base + 0x0018 DSPIx_CTAR3 DSPI clock and transfer attributes register 3 32

Base + 0x001C DSPIx_CTAR4 DSPI clock and transfer attributes register 4 32

Base + 0x0020 DSPIx_CTAR5 DSPI clock and transfer attributes register 5 32

Base + 0x0024 DSPIx_CTAR6 DSPI clock and transfer attributes register 6 32

Base + 0x0028 DSPIx_CTAR7 DSPI clock and transfer attributes register 7 32

Base + 0x002C DSPIx_SR DSPI status register 32

Base + 0x0030 DSPIx_RSER DSPI DMA/interrupt request select and enable register 32

Base + 0x0034 DSPIx_PUSHR DSPI push TX FIFO register 32

Base + 0x0038 DSPIx_POPR DSPI pop RX FIFO register 32

Base + 0x003C DSPIx_TXFR0 DSPI transmit FIFO register 0 32

Base + 0x0040 DSPIx_TXFR1 DSPI transmit FIFO register 1 32

Base + 0x0044 DSPIx_TXFR2 DSPI transmit FIFO register 2 32

Base + 0x0048 DSPIx_TXFR3 DSPI transmit FIFO register 3 32

Base + 0x004C–

Base + 0x0078

— Reserved —

Base + 0x007C DSPIx_RXFR0 DSPI receive FIFO register 0 32

Base + 0x0080 DSPIx_RXFR1 DSPI receive FIFO register 1 32

Base + 0x0084 DSPIx_RXFR2 DSPI receive FIFO register 2 32

Base + 0x0088 DSPIx_RXFR3 DSPI receive FIFO register 3 32

Base + 0x008C–

Base + 0x00B8

— Reserved —

Base + 0x00BC DSPIx_DSICR DSPI DSI configuration register 32

Base + 0x00C0 DSPIx_SDR DSPI DSI serialization data register 32

Base + 0x00C4 DSPIx_ASDR DSPI DSI alternate serialization data register 32

Loading...

Loading...