MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 17-39

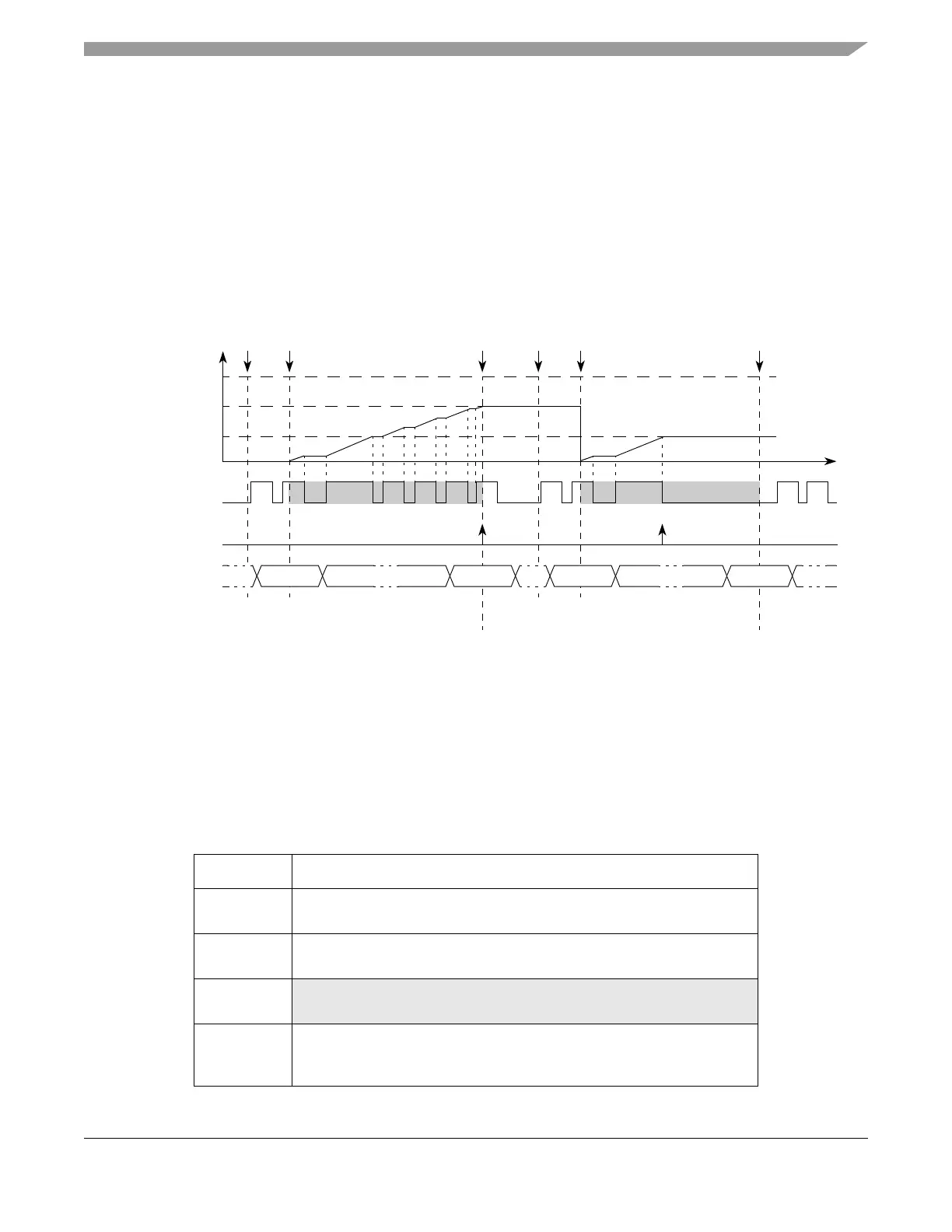

is ready to start counting. The internal counter is used as a time accumulator; that is, it counts up when the

input signal has the same polarity of EDPOL bit in EMIOS_CCRn and does not count otherwise. When a

match occurs in comparator B, the internal counter is disabled regardless of the input signal polarity and

the FLAG bit is set. Reading EMIOS_CCNTRn returns the high or low time of the input signal.

NOTE

The FORCMA and FORCMB bits have no effect when the unified channel

is configured for WPTA mode.

Figure 17-28 shows how the unified channel can be used to accumulate high time.

Figure 17-28. Windowed Programmable Time Accumulation Example

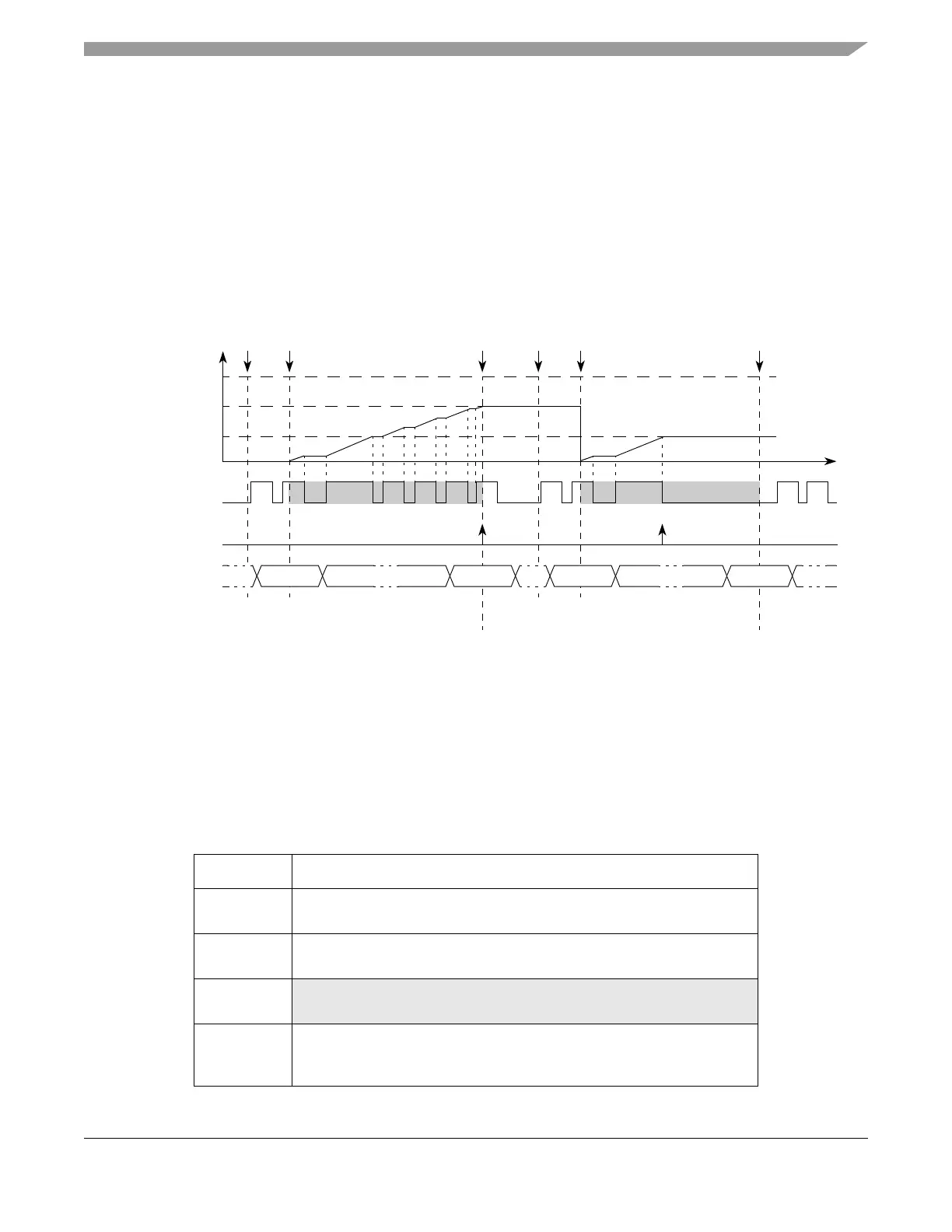

17.4.4.4.11 Modulus Counter Mode (MC)

Table 17-23. Mode of Operation: MC Mode

MODE[0:6] Unified Channel Mode of Operation

0b0010000 Modulus counter

(up counter, internal clock source)

0b0010001 Modulus counter

(up counter, external clock source)

0b0010010–

0b0010011

Reserved

0b0010100 Modulus counter

(up/down counter, no change in counter direction upon match of input

counter and register B1, internal clock source)

A1 Match

Selected

Counter Bus

0x000100 0x000100 0x003000

B1 Value

3

0x001500 0x0042000x001500

0xFFFFFF

Time

FLAG

Set Event

EDPOL = 1

B1 Match

A1 Value

2

Notes:

1

After input filter.

2

Writing EMIOS_CADRn writes to A1.

3

Writing EMIOS_CBDRn writes to B1.

Time

0x000000

Input Signal

1

B1 Match

A1 & B1

Write

0x003000

0x004200

A1 & B1

Write

A1 Match

Accumulator

(EMIOS_CCNTR)

0x000100 0x0042000x001500 0x003000

Loading...

Loading...