MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

A-62 Freescale Semiconductor

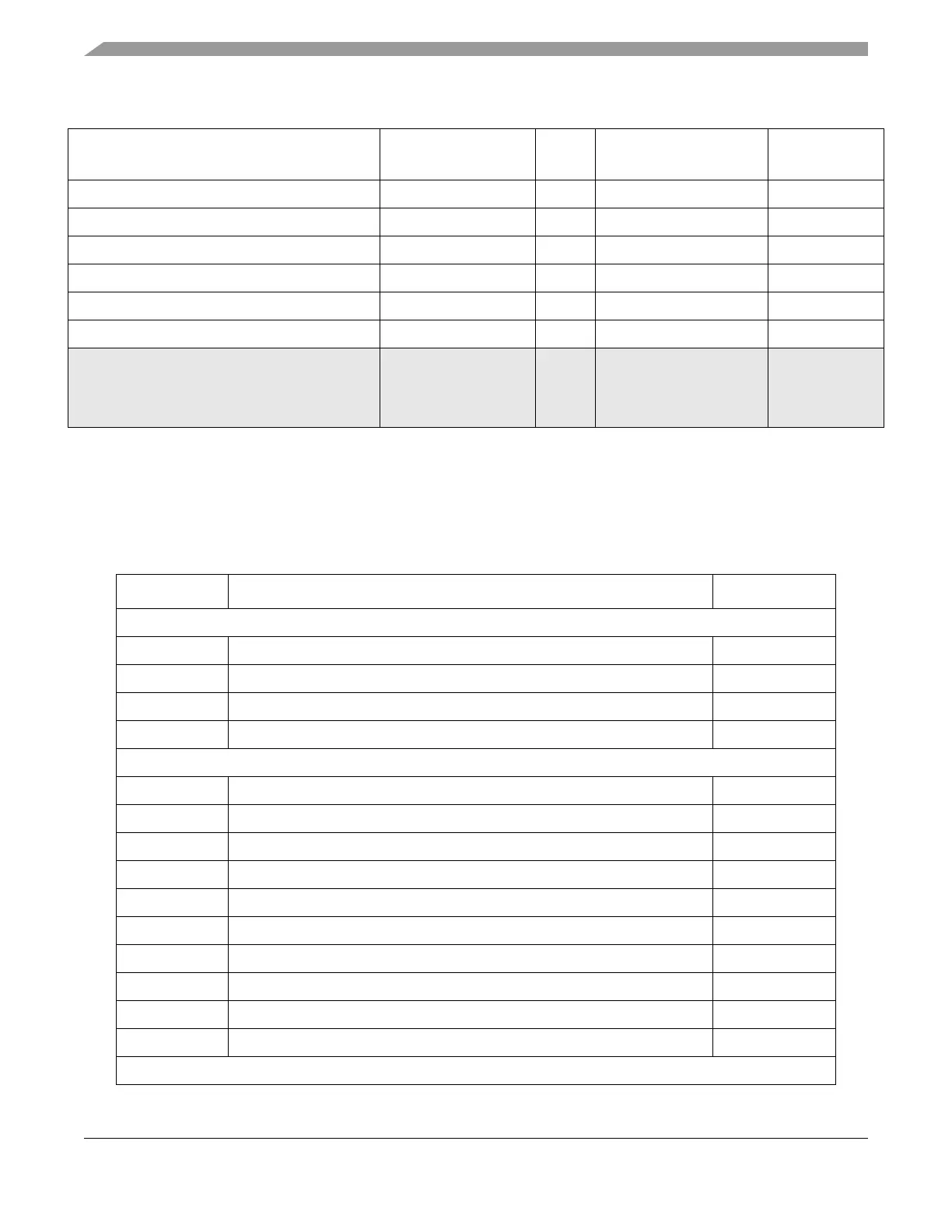

Message buffer 58 MB58 16-bit Base + 0x0420

Message buffer 59 MB59 16-bit Base + 0x0430

Message buffer 60 MB60 16-bit Base + 0x0440

Message buffer 61 MB61 16-bit Base + 0x0450

Message buffer 62 MB62 16-bit Base + 0x0460

Message buffer 63 MB63 16-bit Base + 0x0470

Reserved — — (Base + 0x0480)-

0xFFFC_3FFF (A)

0xFFFC_7FFF (B)

0xFFFF_FFFF (C)

—

1

The registers mapped in the ECSM module (0xFFF4_0014-0xFFF4_001F) provide control and configuration for a software

watchdog timer, and are included as part of a standard Freescale ECSM block incorporated in the MPC5554. The eSys e200z6

core also provides this functionality and is the preferred method for watchdog implementation. In order to optimize code portability

to other members of the eSys MPU family, use of the watchdog registers in the ECSM is not recommended.

2

MPC5554 Only

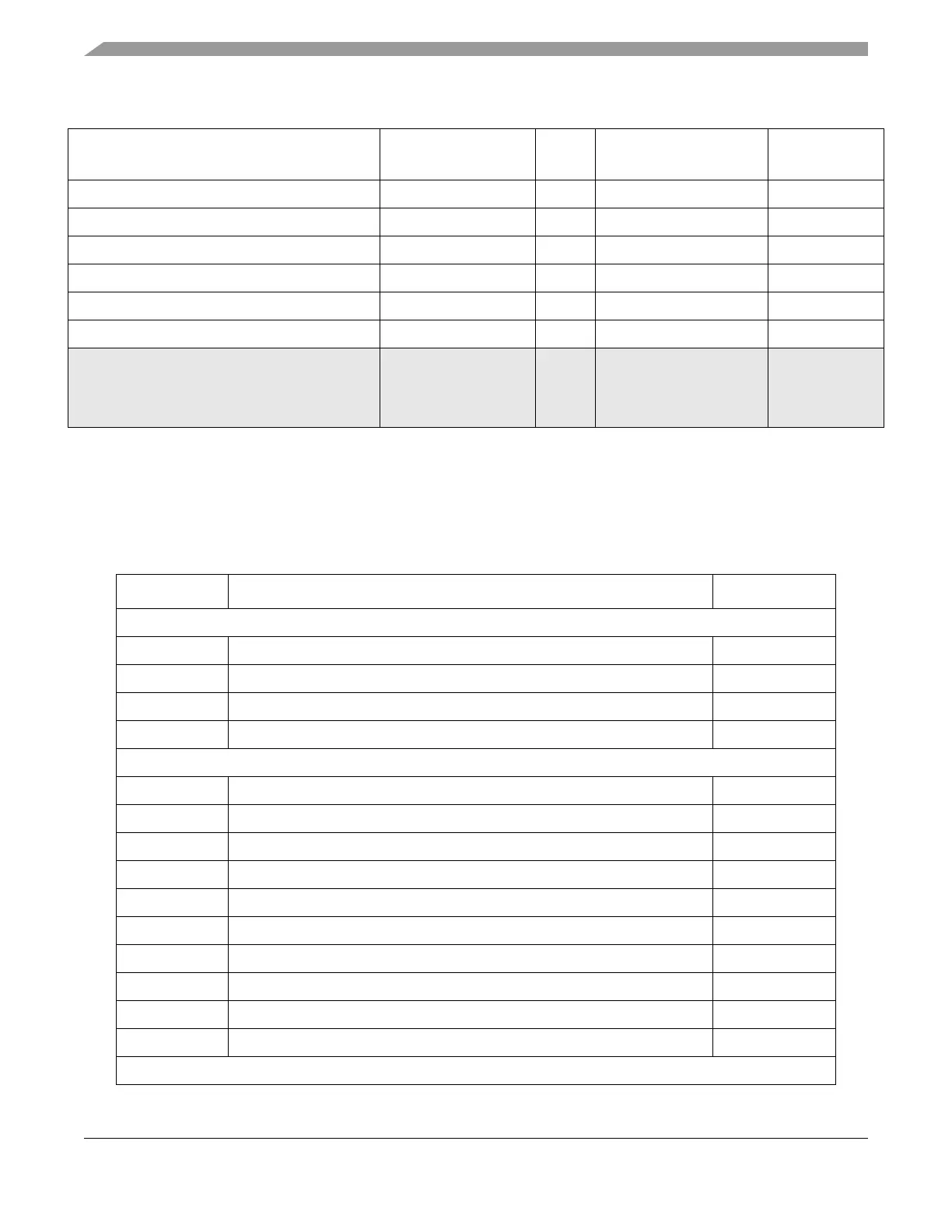

Table A-3. e200z6 Core SPR Numbers (Supervisor Mode)

Register Description SPR (decimal)

General Registers

XER Integer Exception Register 1

LR Link Register 8

CTR Count Register 9

GPR0–GPR31 General Purpose Registers N/A

Special Purpose Registers

SPRG0 Special Purpose Register 0 272

SPRG1 Special Purpose Register 1 273

SPRG2 Special Purpose Register 2 274

SPRG3 Special Purpose Register 3 275

SPRG4 Special Purpose Register 4 276

SPRG5 Special Purpose Register 5 277

SPRG6 Special Purpose Register 6 278

SPRG7 Special Purpose Register 7 279

USPRG0 User Special Purpose Register 256

BUCSR Branch Unit Control and Status Register 1013

Exception Handling/Control Registers

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...