System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 6-5

6.2.1.2 Reset Output (RSTOUT)

The RSTOUT pin is an active-low output that uses a push/pull configuration. The RSTOUT pin is driven

to the low state by the MCU for all internal and external reset sources. After the negation of the RESET

input, RSTOUT

is asserted for 2404 clock cycles; if the PLL is configured for dual-controller mode,

RSTOUT

is asserted for 16004 clocks.

The RSTOUT pin can also be asserted for 2400 clock cycles by a write to the SER bit of the system reset

control register (SIU_SRCR).

NOTE

During an internal power-on-reset (POR), RSTOUT is tri-stated.

6.2.1.3 General-Purpose I/O Pins (GPIO[0:210])

The GPIO pins provide general-purpose input and output function. The GPIO pins are generally

multiplexed with other I/O pin functions. Each GPIO input and output is separately controlled by an

eight-bit input (SIU_GPDI) or output (SIU_GPDO) register. Refer to Section 6.3.1.13, “GPIO Pin Data

Output Registers 0–213 (SIU_GPDOn),” and Section 6.3.1.14, “GPIO Pin Data Input Registers 0–213

(SIU_GPDIn).”

6.2.1.4 Boot Configuration Pins (BOOTCFG[0:1])

The boot configuration pins specify the boot mode initiated by the boot assist module (BAM) program.

BOOTCFG[0:1] are input pins that are sampled 4 clock cycles before the negation of the RSTOUT pin,

and the values latched are stored in the reset status register (SIU_RSR). This occurs for all reset sources

except a debug port reset and a software external reset. The BOOTCFG[0:1] pins are sampled, if the

RSTCFG pin is asserted during reset. Otherwise, if the RSTCFG pin is negated during reset, the

BOOTCFG[0:1] pins are not sampled, the BAM defaults to boot from internal flash, and the BOOTCFG

field in the SIU_RSR is set to the boot from internal flash value (0b00). The latched BOOTCFG[0:1]

values are also driven as output signals from the SIU.

The BOOTCFG pin values are used only if the RSTCFG pin is asserted during the assertion of RSTOUT.

Otherwise, the default values for the BOOTCFG bits in the SIU_RSR are used. For more information on

the default values in the SIU_RSR register, see Section 6.3.1.2, “Reset Status Register (SIU_RSR).

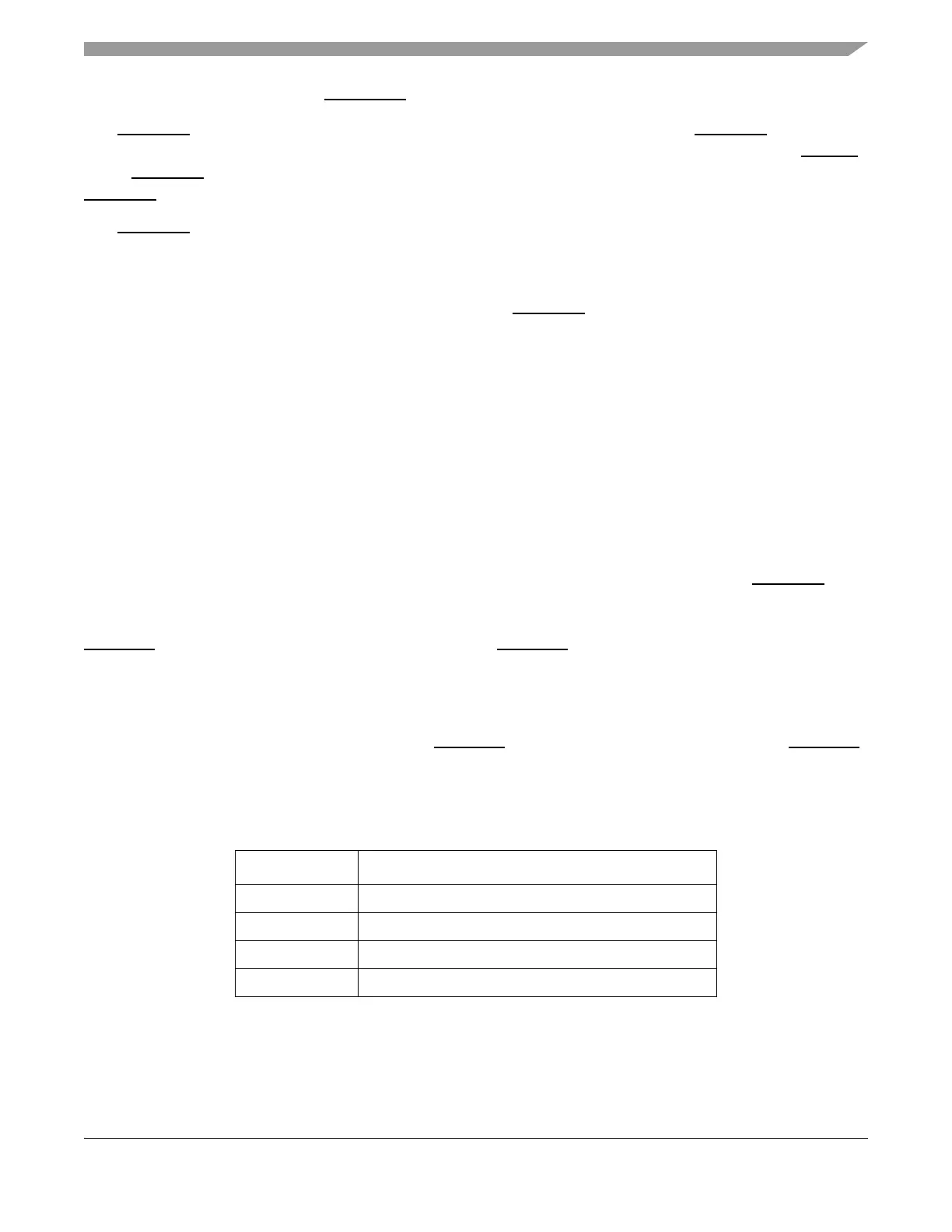

Table 6-2. BOOTCFG[0:1] Configuration

Value Meaning

0b00 Boot from Internal flash memory

0b01 FlexCAN / eSCI bBoot

0b10 Boot from external memory (no arbitration)

0b11 Boot from external memory (external arbitration)

Loading...

Loading...