System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

6-68 Freescale Semiconductor

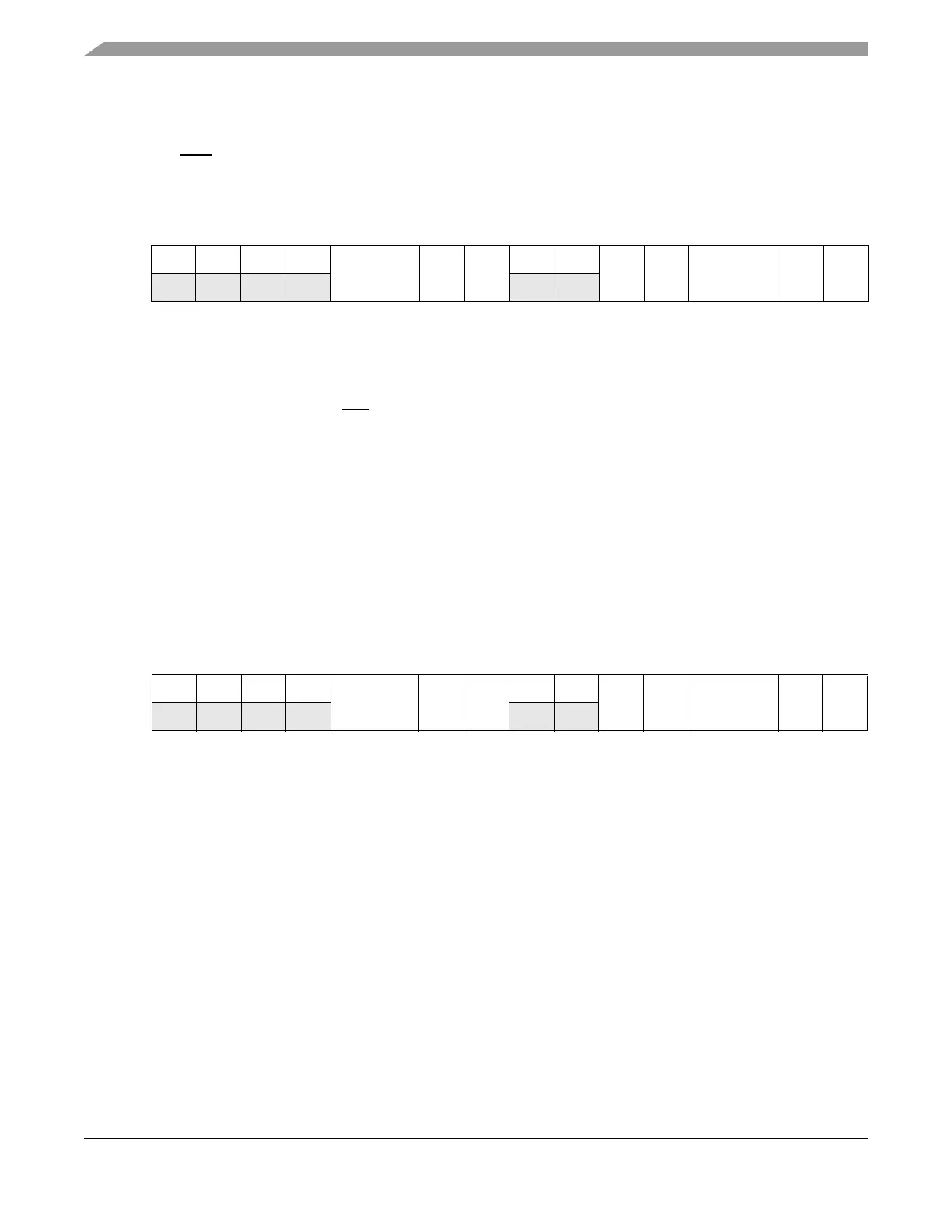

6.3.1.12.68 Pad Configuration Register 113 (SIU_PCR113)

The SIU_PCR113 register controls the pin function, direction, and static electrical attributes of the

TCRCLKA_IRQ[7]_GPIO[113] pin.

Figure 6-80. TCRCLKA_IRQ[7]_GPIO[113] Pad Configuration Register (SIU_PCR113)

Refer to Table 6-16 for bit field definitions.

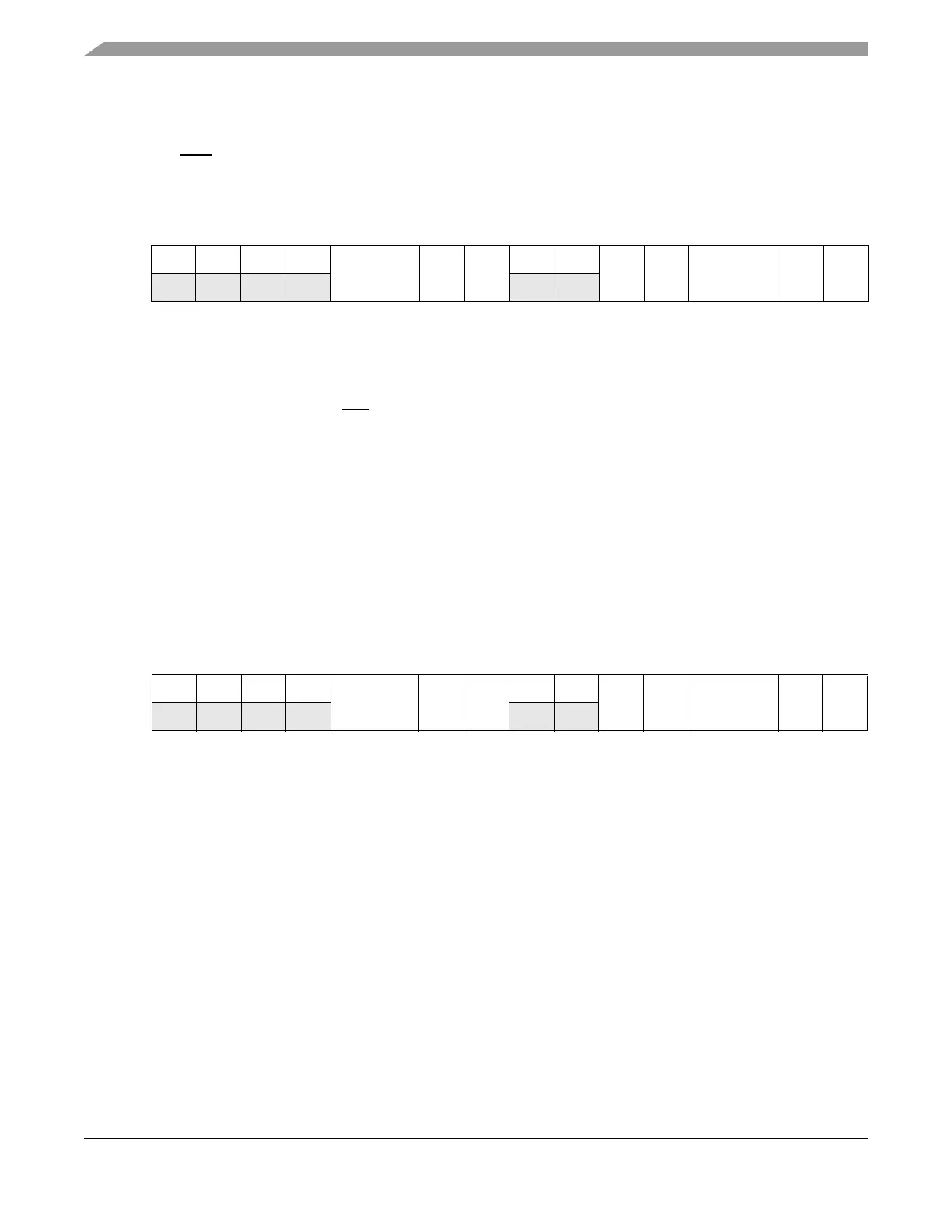

6.3.1.12.69 Pad Configuration Register 114–125 (SIU_PCR114–SIU_PCR125)

The SIU_PCR114–SIU_PCR125 registers control the pin function, direction, and static electrical

attributes of the ETPUA[0:11]_ETPUA[12:23]_GPIO[114:125] pins. Only the output channels of

ETPUA[12:23] are connected to pins. Both the input and output channels of ETPUA[0:11] are connected

to pins.

Figure 6-81. ETPUA[0:11]_ETPUA[12:23]_GPIO[114:125]

Pad Configuration Register (SIU_PCR114–SIU_PCR125)

Refer to Table 6-16 for bit field definitions.

6.3.1.12.70 Pad Configuration Register 126 (SIU_PCR126)

The SIU_PCR126 register controls the pin function, direction, and static electrical attributes of the

ETPUA[12]_PCSB[1]_GPIO[126] pin.

Address: Base + 0x0122 Access: Read / write[4:7, 10:15]

0123456789101112131415

R 0000

PA OBE

1

1

When configured as TCRCLKA or IRQ, the OBE bit has no effect. When configured as GPO, set the OBE bit to 1.

IBE

2

2

When configured as TCRCLKA or IRQ or GPO, set the IBE bit to 1 to reflect the pin state in the corresponding GPDI register.

Clear the IBE to 0 to reduce power consumption. When configured as GPI, set the IBE bit to 1.

00

ODE HYS SRC WPE WPS

W

RESET: 0000000000000011

Address: Base + 0x0124 through Base + 0x013A Access: Read / write[4:7, 10:15]

0123456789101112131415

R 0000

PA OBE

1

1

The OBE bit must be set to 1 for both ETPUA[0:11] and GPIO[114:125] when configured as outputs. When configured as

ETPUA[12:23], the OBE bit has no effect.

IBE

2

2

The IBE bit must be set to 1 for ETPUA[0:11] or GPIO[114:125] when configured as inputs. When configured as ETPUA[12:23],

ETPUA[0:11], or GPIO[114:125] are configured as outputs, set the IBE bit to 1 to reflect the pin state in the corresponding

GPDI register.

00

ODE HYS SRC WPE WPS

W

RESET: 000000000000001U

3

3

The weak pullup/down selection at reset for the ETPUA[0:11] pins is determined by the WKPCFG pin.

Loading...

Loading...