System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

6-100 Freescale Semiconductor

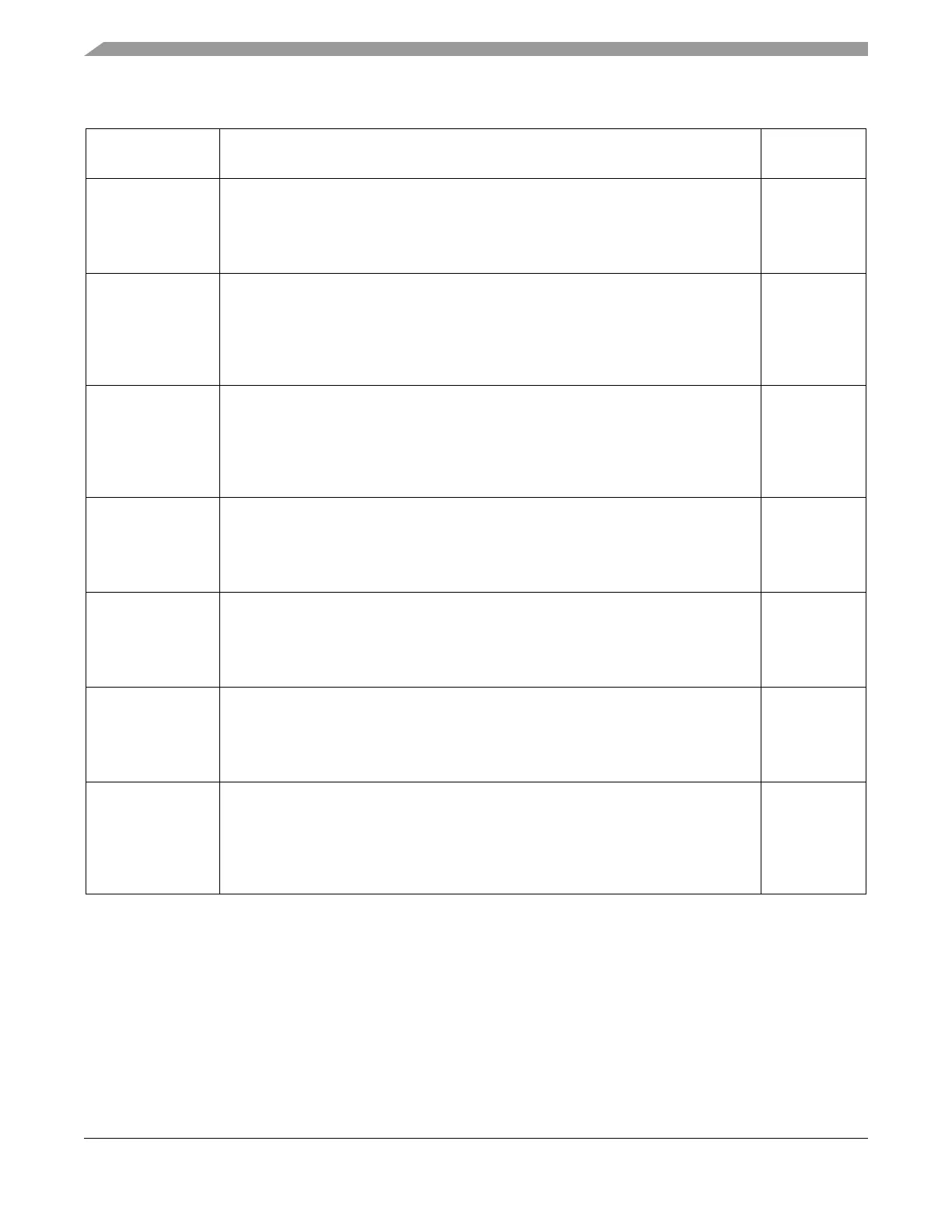

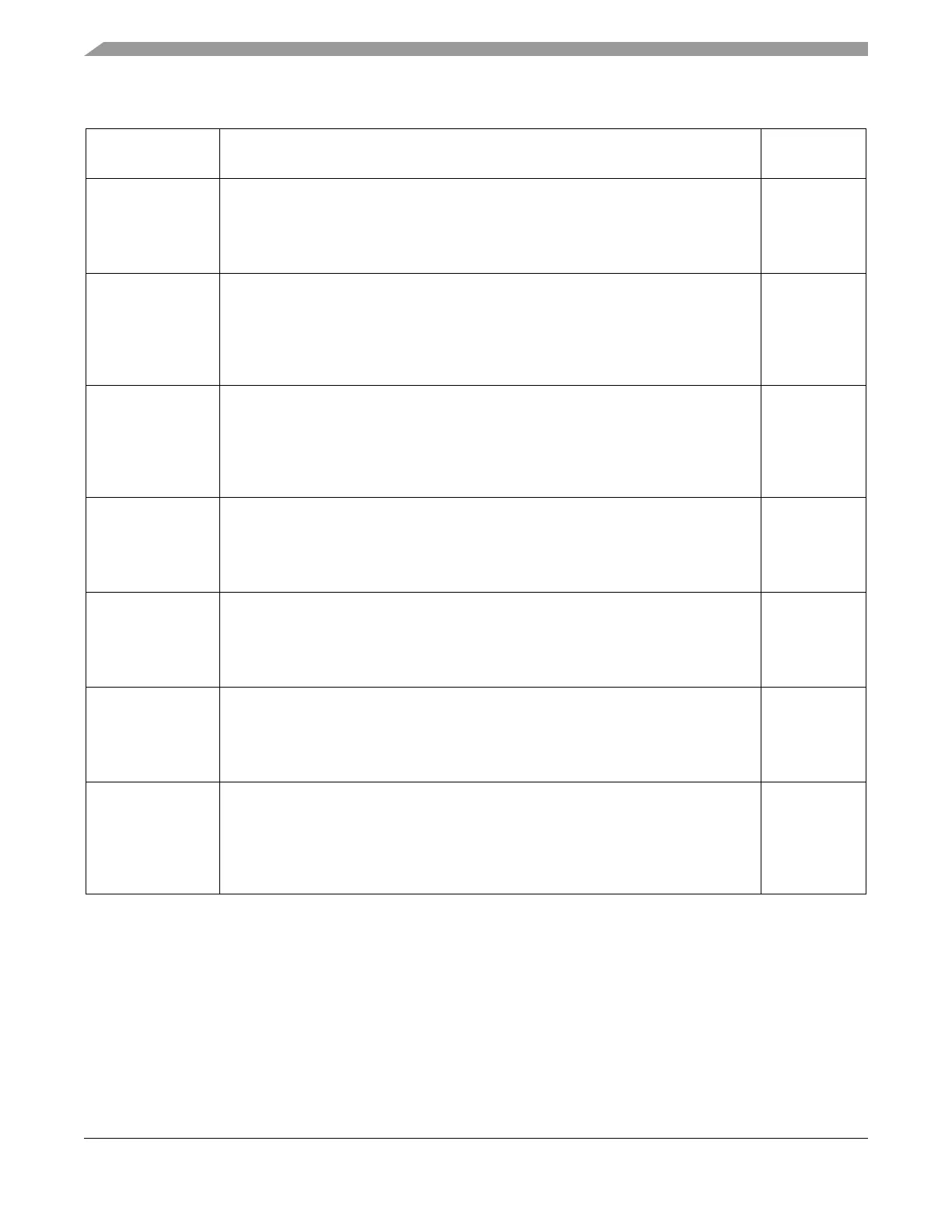

18–19

SSSELC

DSPI C slave select input select. Specifies the source of the DSPI_C slave select input.

00 PCSB[5]_PCSC[0]_GPIO[110] pin

01 PCSA[0] (master)

10 PCSB[0] (master)

11 PCSD[0] (master)

PCSA[0] not

available

20–21

SCKSELC

DSPI C clock input select. Specifies the source of the DSPI_C clock input when in slave

mode.

00 PCSB[4]_SCKC_GPIO[109] pin

01 SCKA (master)

10 SCKB (master)

11 SCKD (master)

SCKA

not available

22–23

TRIGSELC

DSPI C trigger input select. Specifies the source of the DSPI_C trigger input for master

or slave mode.

00 Reserved

01 PCSA[4]

10 PCSB[4]

11 PCSD[4]

PCSA[4]

not available

24–25

SINSELD

DSPI D data input select. Specifies the source of the DSPI_D data input.

00 PCSA[3]_SIND_GPIO[99] pin

01 SOUTA

10 SOUTB

11 SOUTC

PCSA[3] and

SOUTA

not available

26–27

SSSELD

DSPI D slave select input select. Specifies the source of the DSPI_D slave select input.

00 PCSB[1]_PCSD[0]_GPIO[106] pin

01 PCSA[0] (master)

10 PCSB[0] (master)

11 PCSC[0] (master)

PCSA[0] not

available

28–29

SCKSELD

DSPI D clock input select. Specifies the source of the DSPI_D clock input in slave mode.

00 PCSA[2]_SCKD_GPIO[98] pin

01 SCKA (master)

10 SCKB (master)

11 SCKC (master)

PCSA[2] and

SCKA

not available

30–31

TRIGSELD

DSPI D trigger input select. Specifies the source of the DSPI_D trigger input for master

or slave mode.

00 Reserved

01 PCSA[4]

10 PCSB[4]

11 PCSC[4]

PCSA[4] not

available

Table 6-50. SIU_DISR Field Descriptions (continued)

Register Bit Range

Field Name

Description MPC5553

Loading...

Loading...