System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

6-102 Freescale Semiconductor

6.3.1.19 External Clock Control Register (SIU_ECCR)

The SIU_ECCR controls the timing relationship between the system clock and the external clocks

ENGCLK and CLKOUT. All bits and fields in the SIU_ECCR are read/write and are reset by the

synchronous reset signal.

Address: Base + 0x0984 Access: Read / write[18:23, 28, 30:31]

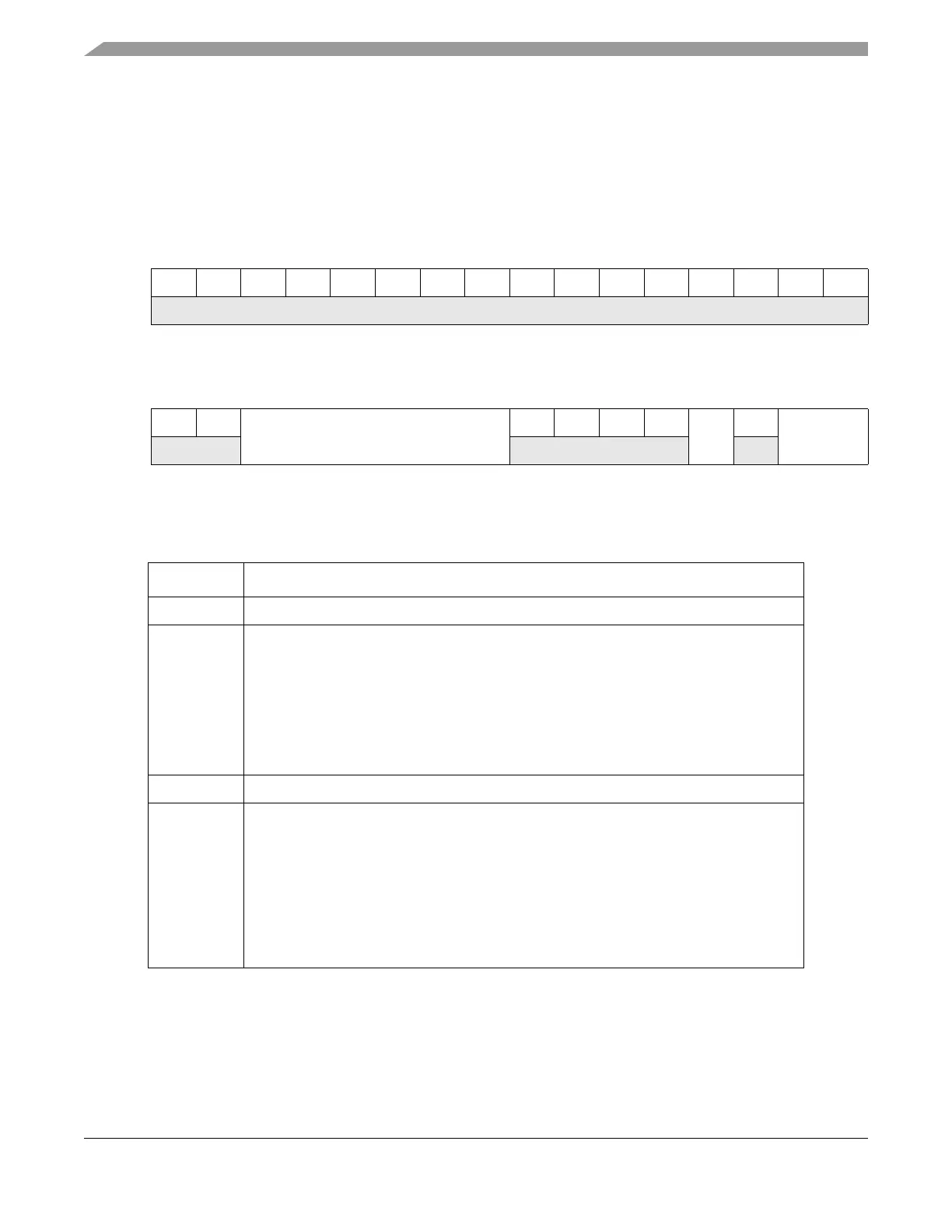

0123456789101112131415

R

0000000000000000

W

Reset

0000000000000000

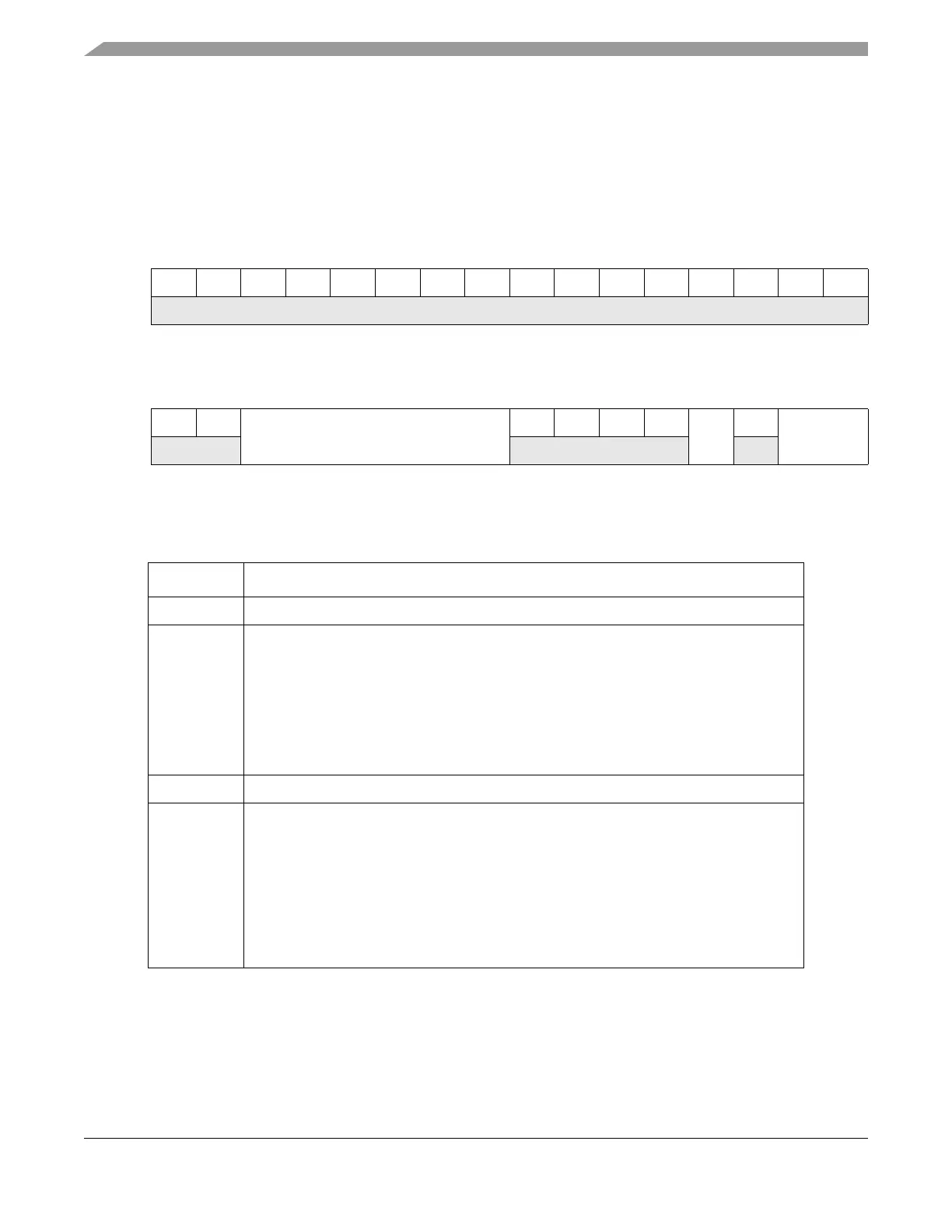

Address: Base + 0x0984 Access: Read / write[18:23, 28, 30:31]

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

00

ENGDIV

0000

EBTS

0

EBDF

W

Reset

0001000000000001

Figure 6-136. External Clock Control Register (SIU_ECCR)

Table 6-52. SIU_ECCR Field Descriptions

Name Description

0–17

Reserved.

18–23

ENGDIV

[0:5]

Engineering clock division factor. Specifies the frequency ratio between the system clock

and ENGCLK. The ENGCLK frequency is divided by the system clock frequency according

to the equation:

Note: Clearing ENGDIV to 0 is reserved. Synchronization between ENGCLK and

CLKOUT cannot be guaranteed.

24–27

Reserved.

28

EBTS

External bus tap select. Changes the phase relationship between the system clock and

CLKOUT. Changing the phase relationship so that CLKOUT is advanced in relation to the

system clock increases the output hold time of the external bus signals to a non-zero value.

It also increases the output delay times, increases the input hold times to non-zero values,

and decreases the input setup times. Refer to the Electrical Specifications for how the

EBTS bit affects the external bus timing.

0 External bus signals have zero output hold times.

1 External bus signals have non-zero output hold times.

Note: The EBTS bit must not be modified while an external bus transaction is in progress.

Engineering clock frequency

System clock frequency

ENGDIV 2

---------------------------------------------------------------=

Loading...

Loading...