MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 9-11

point of the fault. If a bus error occurs on the last read prior to beginning the write sequence, the write will

execute using the data captured during the bus error. If a bus error occurs on the last write prior to switching

to the next read sequence, the read sequence will execute before the channel is terminated due to the

destination bus error.

The occurrence of any type of error causes the eDMA engine to stop the active channel, and the appropriate

channel bit in the eDMA error register to be asserted. At the same time, the details of the error condition

are loaded into the EDMA_ESR. The major loop complete indicators, setting the transfer control

descriptor DONE flag and the possible assertion of an interrupt request, are not affected when an error is

detected. After the error status has been updated, the eDMA engine continues to operate by servicing the

next appropriate channel. A channel that experiences an error condition is not automatically disabled. If a

channel is terminated by an error and then issues another service request before the error is fixed, that

channel will execute and terminate with the same error condition.

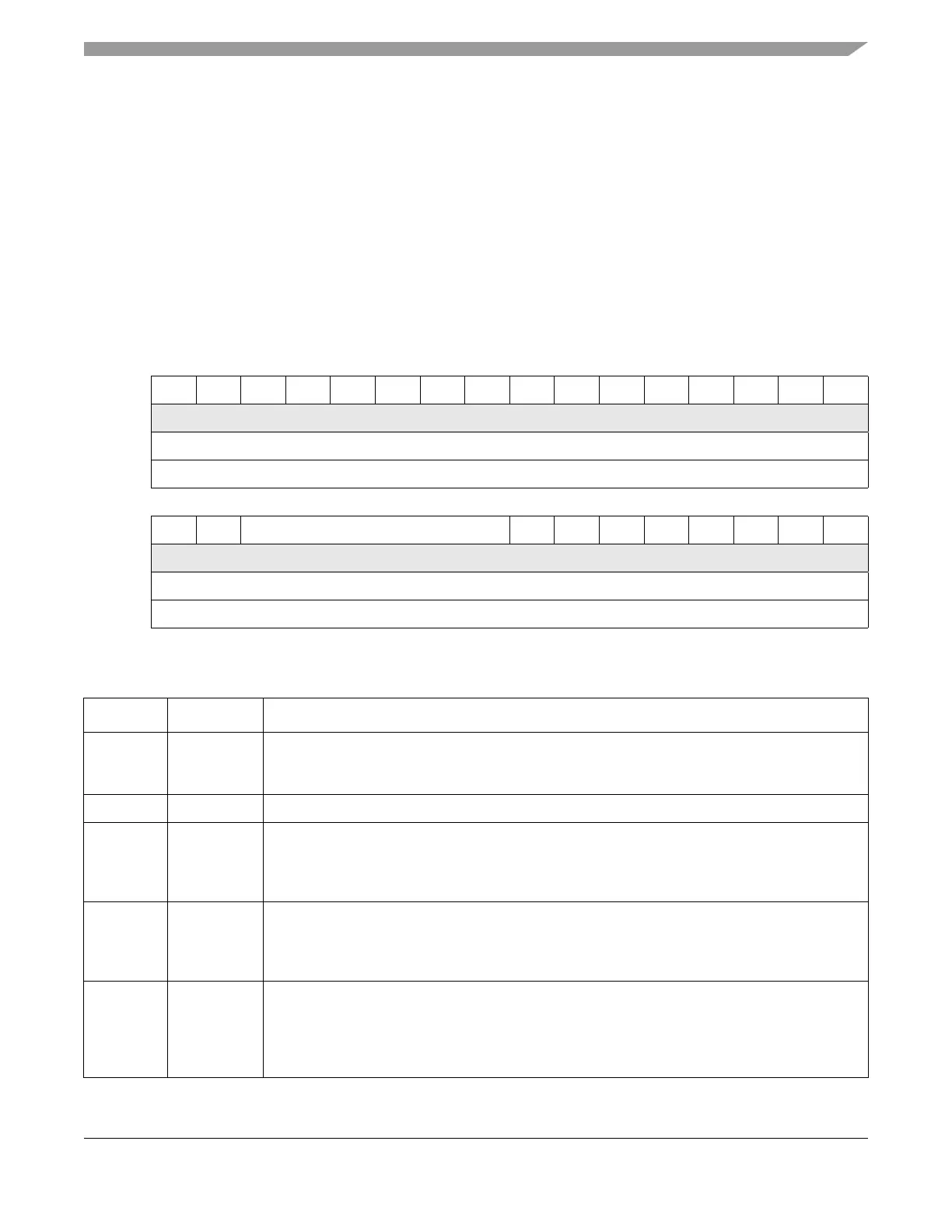

0123456789101112131415

RVLD000000000000000

W

Reset0000000000000000

Reg Addr Base + 0x0004

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R GPE CPE ERRCHN SAE SOE DAE DOE NCE SGE SBE DBE

W

Reset0000000000000000

Reg Addr Base + 0x0004

Figure 9-3. eDMA Error Status Register (EDMA_ESR)

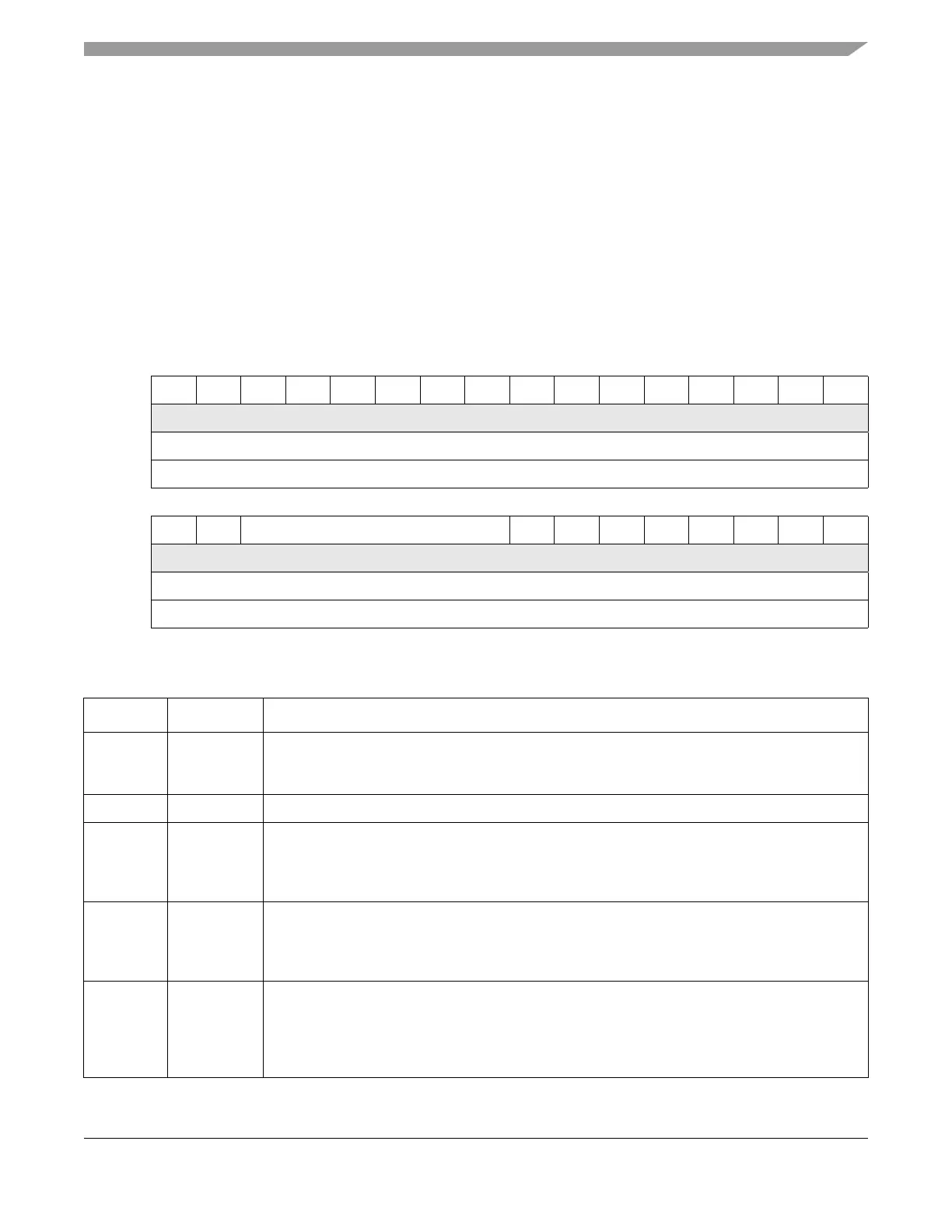

Table 9-3. EDMA_ESR Field Descriptions

Bits Name Description

0 VLD Logical OR of all EDMA_ERH and EDMA_ERL status bits.

0 No EDMA_ER bits are set.

1 At least one EDMA_ER bit is set indicating a valid error exists that has not been cleared.

1–15 — Reserved.

16 GPE Group priority error.

0 No group priority error.

1 The last recorded error was a configuration error among the group priorities indicating not all

group priorities are unique.

17 CPE Channel priority error.

0 No channel priority error.

1 The last recorded error was a configuration error in the channel priorities within a group,

indicating not all channel priorities within a group are unique.

18–23 ERRCHN

[0:5]

Error channel number — this is the channel number of the last recorded error (excluding GPE and

CPE errors)

Note: Do not rely on the number in the ERRCHN field for group and channel priority errors. Group

and channel priority errors need to be resolved by inspection. The application code must

interrogate the priority registers to find groups or channels with duplicate priority level.

Loading...

Loading...