MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 9-29

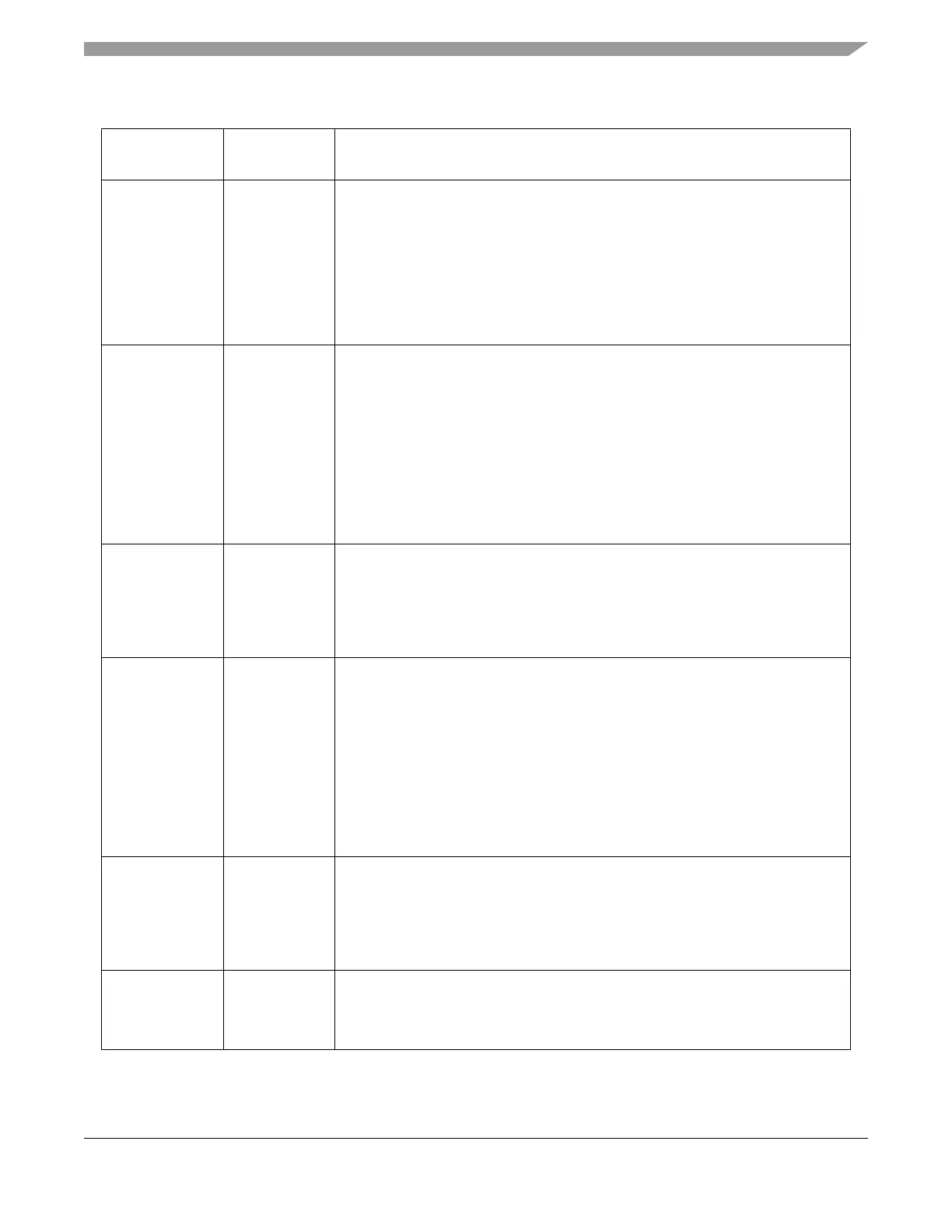

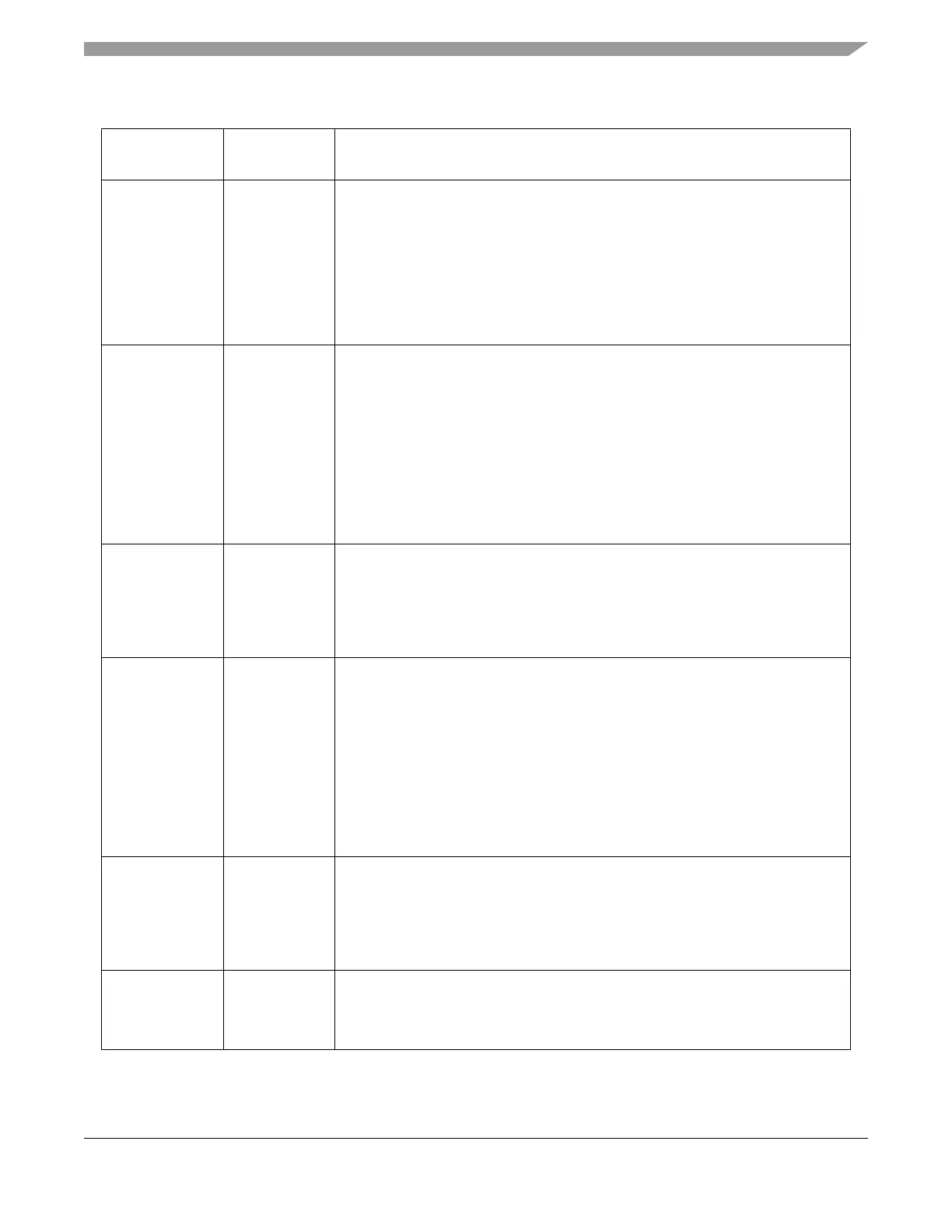

250 /

0x1C [26]

MAJOR.E_LINK Enable channel-to-channel linking on major loop completion. As the channel

completes the outer major loop, this flag enables the linking to another channel,

defined by MAJOR.LINKCH[0:5]. The link target channel initiates a channel service

request via an internal mechanism that sets the TCD.START bit of the specified

channel.

NOTE: To support the dynamic linking coherency model, this field is forced to zero

when written to while the TCD.DONE bit is set.

0 The channel-to-channel linking is disabled.

1 The channel-to-channel linking is enabled.

251 /

0x1C [27]

E_SG Enable scatter/gather processing. As the channel completes the outer major loop,

this flag enables scatter/gather processing in the current channel. If enabled, the

eDMA engine uses DLAST_SGA as a memory pointer to a 0-modulo-32 address

containing a 32-byte data structure which is loaded as the transfer control

descriptor into the local memory.

NOTE: To support the dynamic scatter/gather coherency model, this field is forced

to zero when written to while the TCD.DONE bit is set.

0 The current channel’s TCD is “normal” format.

1 The current channel’s TCD specifies a scatter gather format. The DLAST_SGA

field provides a memory pointer to the next TCD to be loaded into this channel

after the outer major loop completes its execution.

252 /

0x1C [28]

D_REQ Disable hardware request. If this flag is set, the eDMA hardware automatically

clears the corresponding EDMA_ERQH or EDMA_ERQL bit when the current

major iteration count reaches zero.

0 The channel’s EDMA_ERQH or EDMA_ERQL bit is not affected.

1 The channel’s EDMA_ERQH or EDMA_ERQL bit is cleared when the outer

major loop is complete.

253 /

0x1C [29]

INT_HALF Enable an interrupt when major counter is half complete. If this flag is set, the

channel generates an interrupt request by setting the appropriate bit in the

EDMA_ERQH or EDMA_ERQL when the current major iteration count reaches the

halfway point. Specifically, the comparison performed by the eDMA engine is

(CITER == (BITER >> 1)). This halfway point interrupt request is provided to

support double-buffered (aka ping-pong) schemes, or other types of data

movement where the processor needs an early indication of the transfer’s progress.

CITER = BITER = 1 with INT_HALF enabled will generate an interrupt as it satisfies

the equation (CITER == (BITER >> 1)) after a single activation.

0 The half-point interrupt is disabled.

1 The half-point interrupt is enabled.

254 /

0x1C [30]

INT_MAJ Enable an interrupt when major iteration count completes. If this flag is set, the

channel generates an interrupt request by setting the appropriate bit in the

EDMA_ERQH or EDMA_ERQL when the current major iteration count reaches

zero.

0 The end-of-major loop interrupt is disabled.

1 The end-of-major loop interrupt is enabled.

255 /

0x1C [31]

START Channel start. If this flag is set, the channel is requesting service. The eDMA

hardware automatically clears this flag after the channel begins execution.

0 The channel is not explicitly started.

1 The channel is explicitly started via a software initiated service request.

Table 9-18. TCDn Field Descriptions (Continued)

Bits /

Word Offset [n:n]

Name Description

Loading...

Loading...