MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 9-33

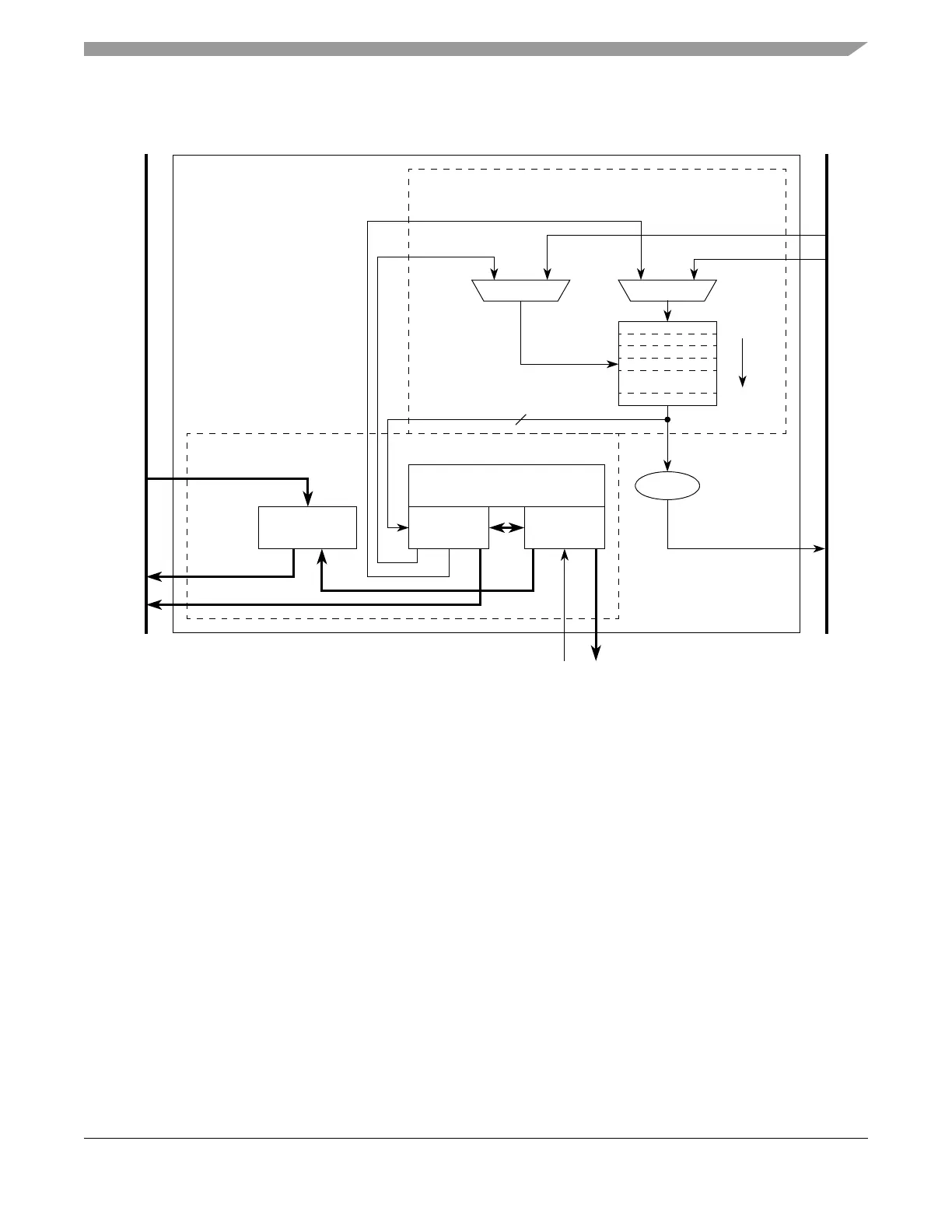

This source read/destination write processing continues until the inner minor byte count has been

transferred. The eDMA Done Handshake signal is asserted at the end of the minor byte count transfer.

Figure 9-23. eDMA Operation, Part 2

After the inner minor byte count has been moved, the final phase of the basic data flow is performed. In

this segment, the address path logic performs the required updates to certain fields in the channel’s TCD:

for example., SADDR, DADDR, CITER. If the outer major iteration count is exhausted, then there are

additional operations which are performed. These include the final address adjustments and reloading of

the BITER field into the CITER. Additionally, assertion of an optional interrupt request occurs at this time,

as does a possible fetch of a new TCD from memory using the scatter/gather address pointer included in

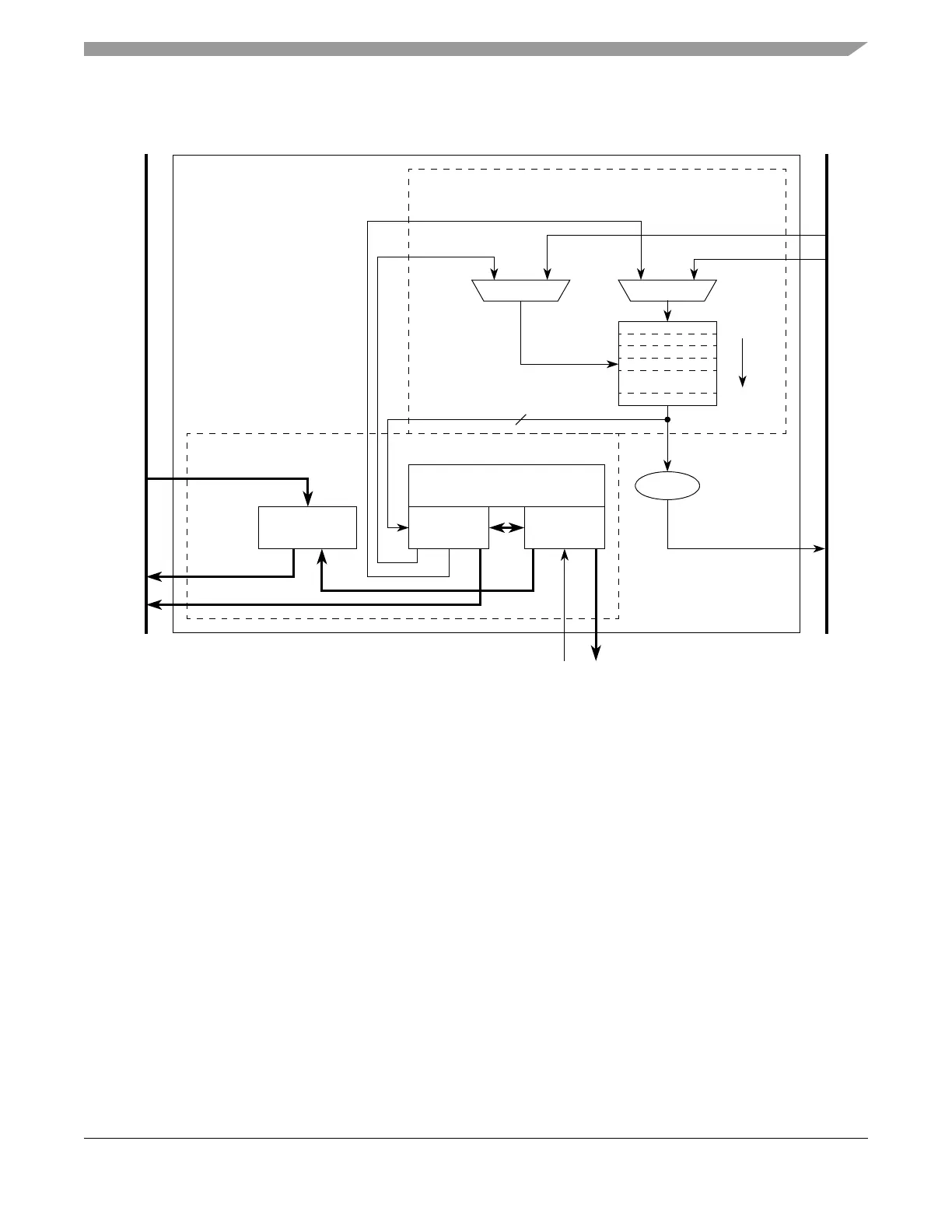

Slave Interface

eDMA

eDMA Interrupt Request

System Bus

Program Model/

Slave Write Data

Slave Write Address

Bus Write Data

Slave Read Data

Bus Address

eDMA Engine

TCD0

TCDn-1*

eDMA Peripheral

Bus Read Data

Channel Arbitration

Request

SRAM

Transfer Control Descriptor

(TCD)

SRAM

* n = 64 channels in MPC5554

32 channels in MPC5553

Data Path

Control

Address

Path

eDMA Done Handshake

Loading...

Loading...