MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 10-9

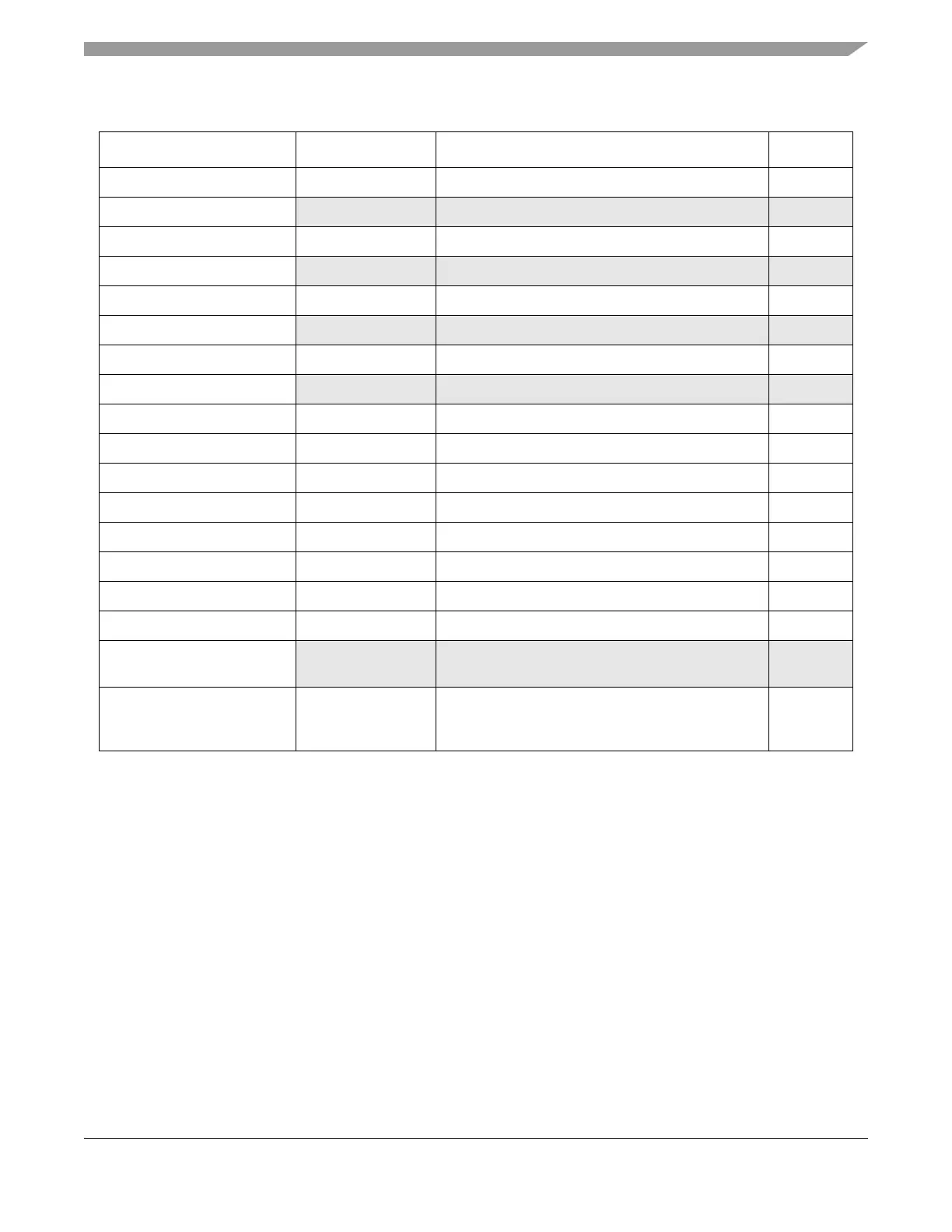

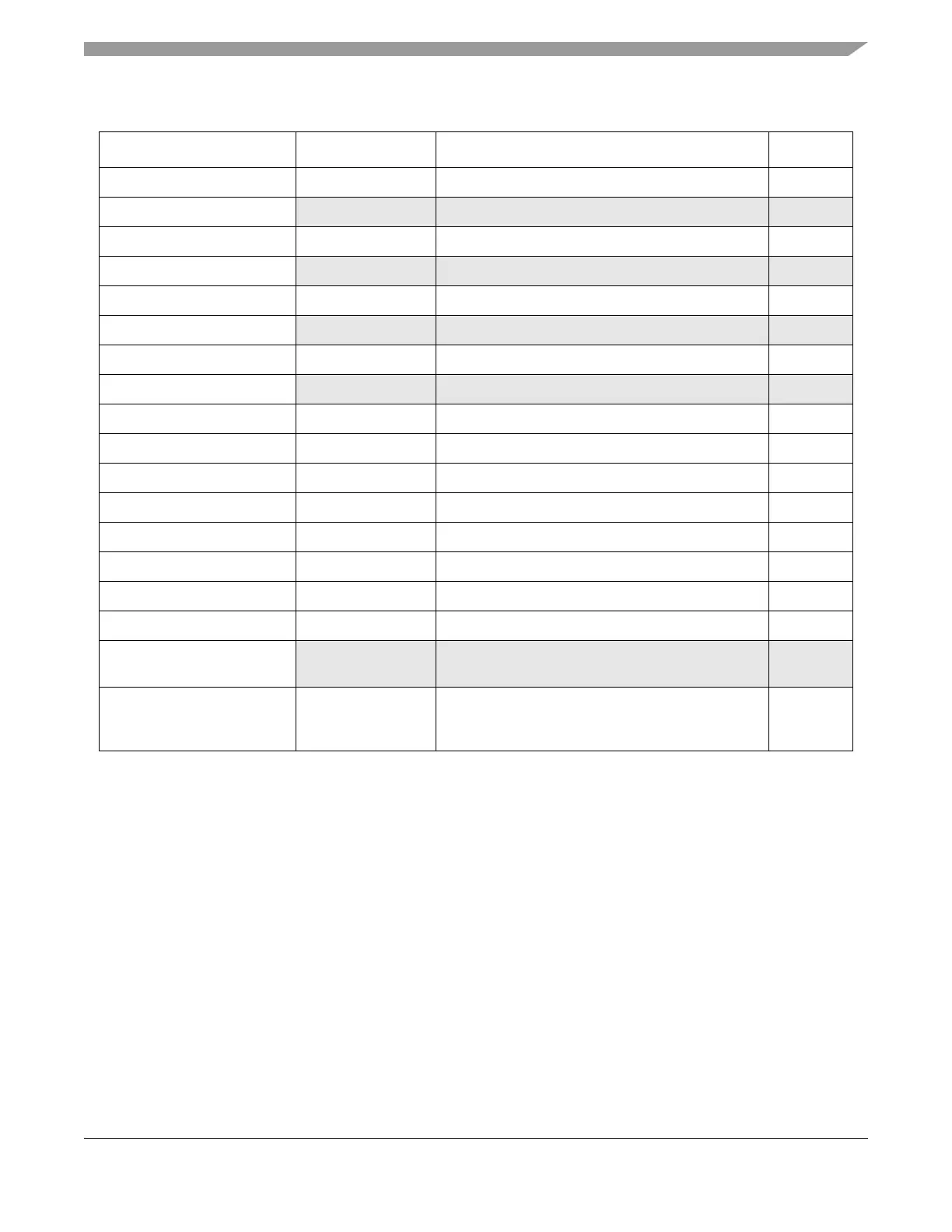

Table 10-2. INTC Memory Map

Address Register Name Register Description Size (bits)

Base (0xFFF4_8000) INTC_MCR INTC module configuration register 32

Base + 0x0004

— Reserved —

Base + 0x0008 INTC_CPR INTC current priority register 32

Base + 0x000C

— Reserved —

Base + 0x0010 INTC_IACKR INTC interrupt acknowledge register

1

1

When the HVEN bit in the INTC_MCR is set, a read of the INTC_IACKR has no effect.

32

Base + 0x0014

— Reserved —

Base + 0x0018 INTC_EOIR INTC end-of-interrupt register 32

Base + 0x001C

— Reserved —

Base + 0x0020 INTC_SSCIR0 INTC software set/clear interrupt register 0 8

Base + 0x0021 INTC_SSCIR1 INTC software set/clear interrupt register 1 8

Base + 0x0022 INTC_SSCIR2 INTC software set/clear interrupt register 2 8

Base + 0x0023 INTC_SSCIR3 INTC software set/clear interrupt register 3 8

Base + 0x0024 INTC_SSCIR4 INTC software set/clear interrupt register 4 8

Base + 0x0025 INTC_SSCIR5 INTC software set/clear interrupt register 5 8

Base + 0x0026 INTC_SSCIR6 INTC software set/clear interrupt register 6 8

Base + 0x0027 INTC_SSCIR7 INTC software set/clear interrupt register 7 8

Base + 0x0028–

Base + 0x003C

— Reserved —

Base + 0x0040–

Base + 0x0173 (MPC5554) or

Base + 0x0110 (MPC5553)

INTC_PSRn INTC priority select register 0–307 (MPC5554)

2

INTC priority select register 0–211 (MPC5553)

3

2

In the MPC5554, the PRI fields are reserved for peripheral interrupt requests whose vectors are 147, 148, 150, 151, 154,

175, 194–201, 282 and 301–307.

3

In the MPC5553, the PRI fields are reserved for peripheral interrupt requests whose vectors are 147, 148, 150, 151, 154,

175, 197-201, 210, 211.

NOTE

To ensure compatibility with all PowerPC processorss, the TLB entry

covering the INTC memory map must be configured as guarded, both

in software and hardware vector modes.

• In software vector mode, the INTC_IACKR must not be read

speculatively.

• In hardware vector mode, guarded writes to the INTC_CPR or

INTC_EOIR complete before the interrupt acknowledge signal

from the processor asserts.

8

Loading...

Loading...