MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 10-17

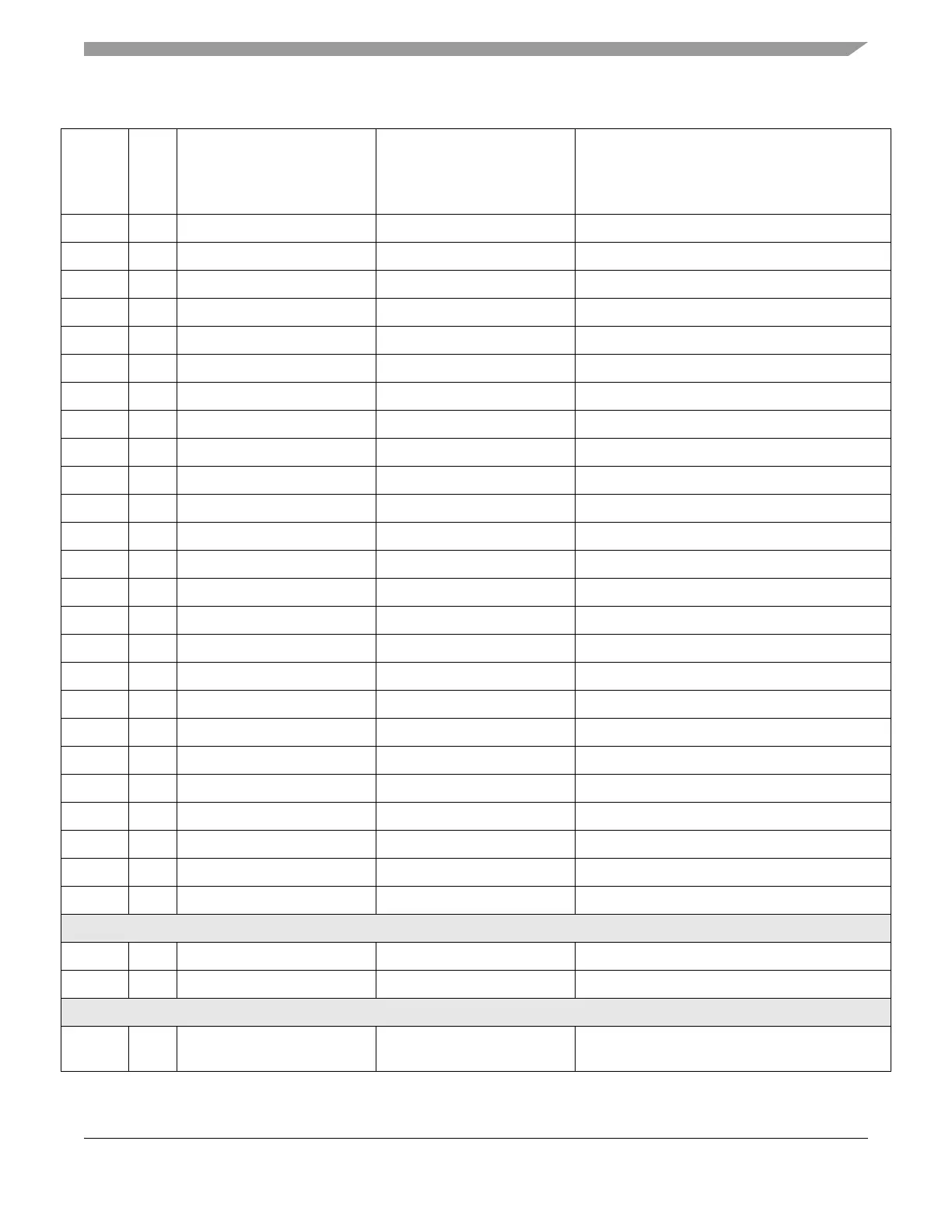

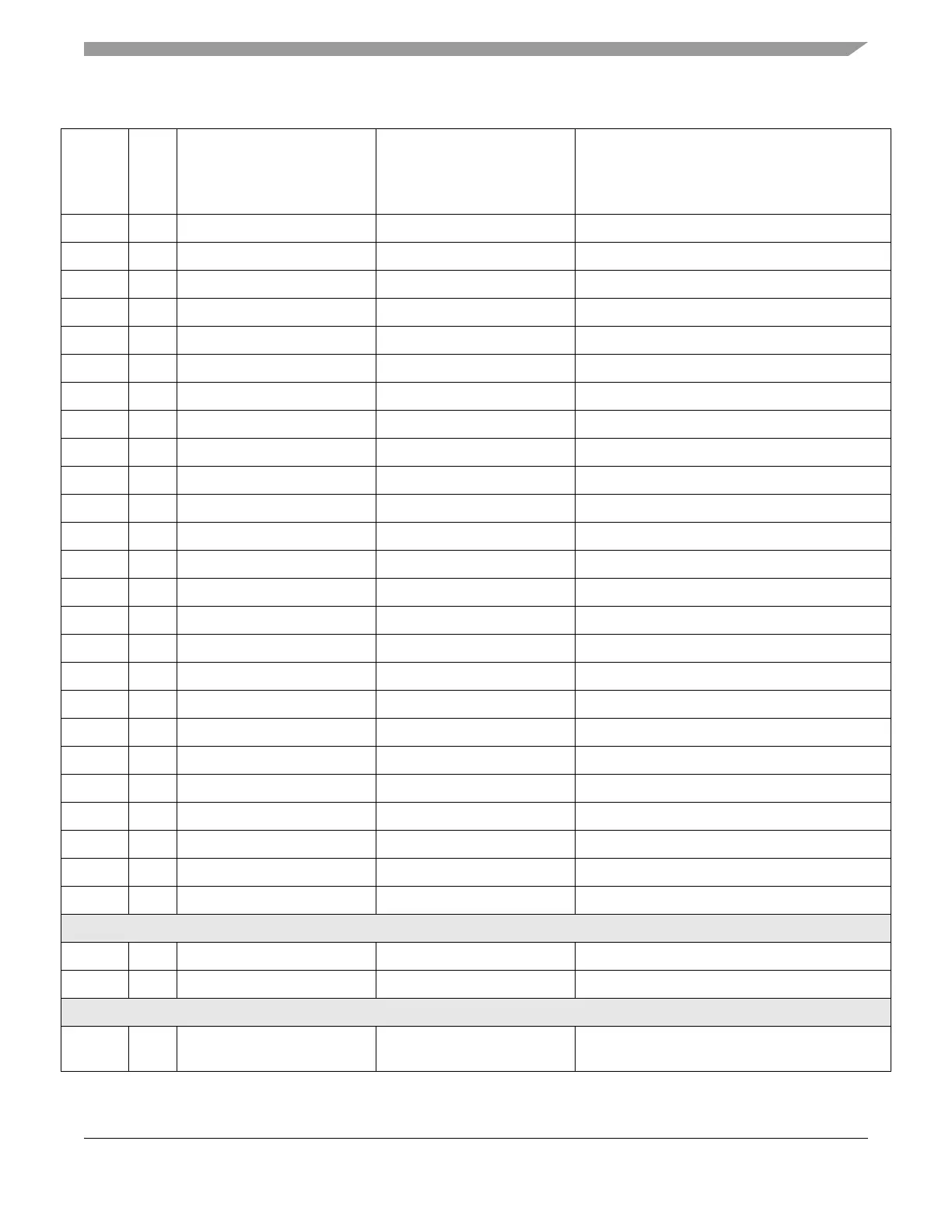

0x0120 18 EDMA_IRQRL[INT07] EDMA_IRQRL[INT07] eDMA channel Interrupt 7

0x0130 19 EDMA_IRQRL[INT08] EDMA_IRQRL[INT08] eDMA channel Interrupt 8

0x0140 20 EDMA_IRQRL[INT09] EDMA_IRQRL[INT09] eDMA channel Interrupt 9

0x0150 21 EDMA_IRQRL[INT10] EDMA_IRQRL[INT10] eDMA channel Interrupt 10

0x0160 22 EDMA_IRQRL[INT11] EDMA_IRQRL[INT11] eDMA channel Interrupt 11

0x0170 23 EDMA_IRQRL[INT12] EDMA_IRQRL[INT12] eDMA channel Interrupt 12

0x0180 24 EDMA_IRQRL[INT13] EDMA_IRQRL[INT13] eDMA channel Interrupt 13

0x0190 25 EDMA_IRQRL[INT14] EDMA_IRQRL[INT14] eDMA channel Interrupt 14

0x01A0 26 EDMA_IRQRL[INT15] EDMA_IRQRL[INT15] eDMA channel Interrupt 15

0x01B0 27 EDMA_IRQRL[INT16] EDMA_IRQRL[INT16] eDMA channel Interrupt 16

0x01C0 28 EDMA_IRQRL[INT17] EDMA_IRQRL[INT17] eDMA channel Interrupt 17

0x01D0 29 EDMA_IRQRL[INT18] EDMA_IRQRL[INT18] eDMA channel Interrupt 18

0x01E0 30 EDMA_IRQRL[INT19] EDMA_IRQRL[INT19] eDMA channel Interrupt 19

0x01F0 31 EDMA_IRQRL[INT20] EDMA_IRQRL[INT20] eDMA channel Interrupt 20

0x0200 32 EDMA_IRQRL[INT21] EDMA_IRQRL[INT21] eDMA channel Interrupt 21

0x0210 33 EDMA_IRQRL[INT22] EDMA_IRQRL[INT22] eDMA channel Interrupt 22

0x0220 34 EDMA_IRQRL[INT23] EDMA_IRQRL[INT23] eDMA channel Interrupt 23

0x0230 35 EDMA_IRQRL[INT24] EDMA_IRQRL[INT24] eDMA channel Interrupt 24

0x0240 36 EDMA_IRQRL[INT25] EDMA_IRQRL[INT25] eDMA channel Interrupt 25

0x0250 37 EDMA_IRQRL[INT26] EDMA_IRQRL[INT26] eDMA channel Interrupt 26

0x0260 38 EDMA_IRQRL[INT27] EDMA_IRQRL[INT27] eDMA channel Interrupt 27

0x0270 39 EDMA_IRQRL[INT28] EDMA_IRQRL[INT28] eDMA channel Interrupt 28

0x0280 40 EDMA_IRQRL[INT29] EDMA_IRQRL[INT29] eDMA channel Interrupt 29

0x0290 41 EDMA_IRQRL[INT30] EDMA_IRQRL[INT30] eDMA channel Interrupt 30

0x02A0 42 EDMA_IRQRL[INT31] EDMA_IRQRL[INT31] eDMA channel Interrupt 31

PLL

0x02B0 43 FMPLL_SYNSR[LOCF] FMPLL_SYNSR[LOCF] FMPLL Loss of Clock Flag

0x02C0 44 FMPLL_SYNSR[LOLF] FMPLL_SYNSR[LOLF] FMPLL Loss of Lock Flag

SIU

0x02D0 45 SIU_OSR[OVF15:OVF0] SIU_OSR[OVF15:OVF0] SIU combined overrun interrupt requests of the

external interrupt Overrun Flags

Table 10-9. INTC: Interrupt Request Sources (Continued)

Hardware

Vector

Mode

Offset

Vector

Source

1

MPC5553

Source

1

MPC5554

Description

Loading...

Loading...