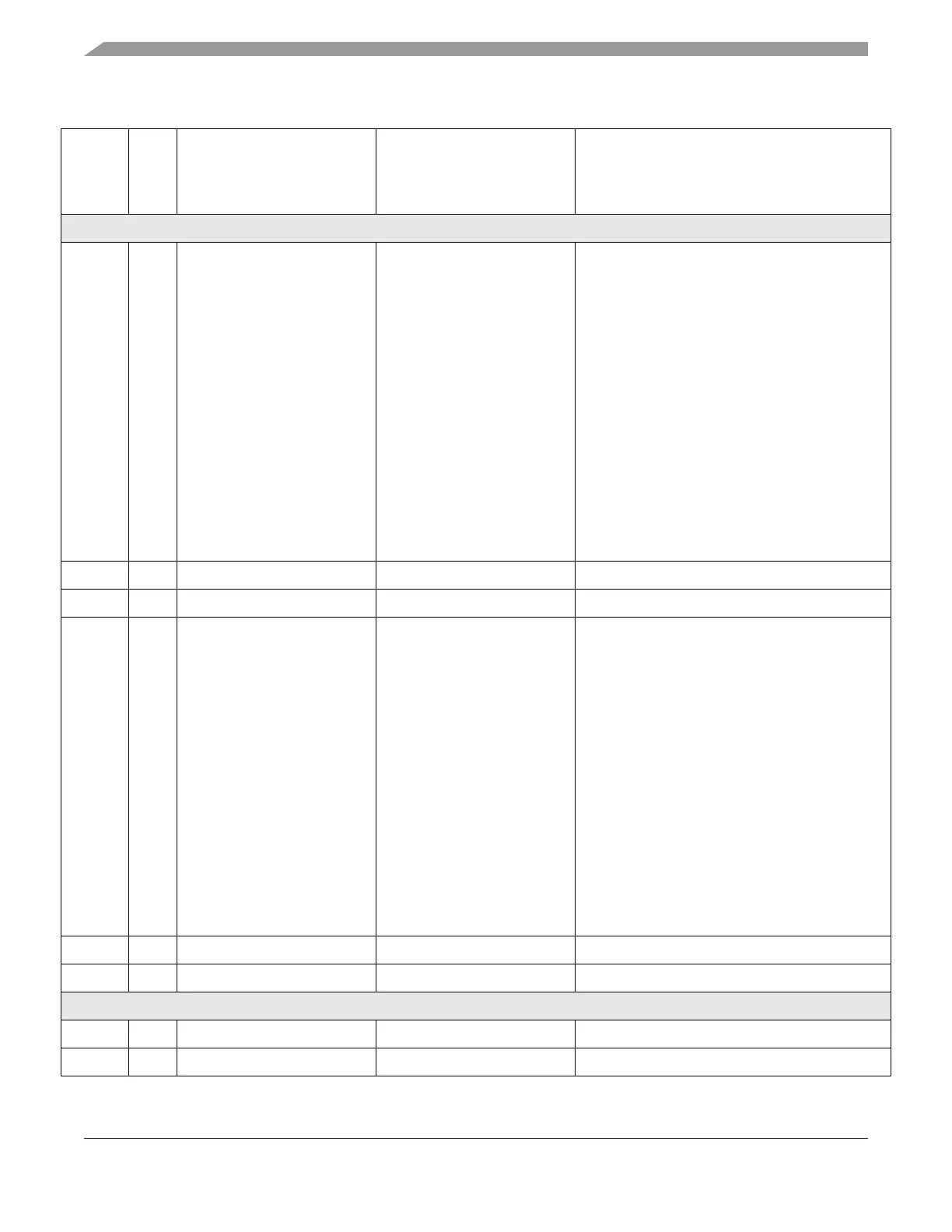

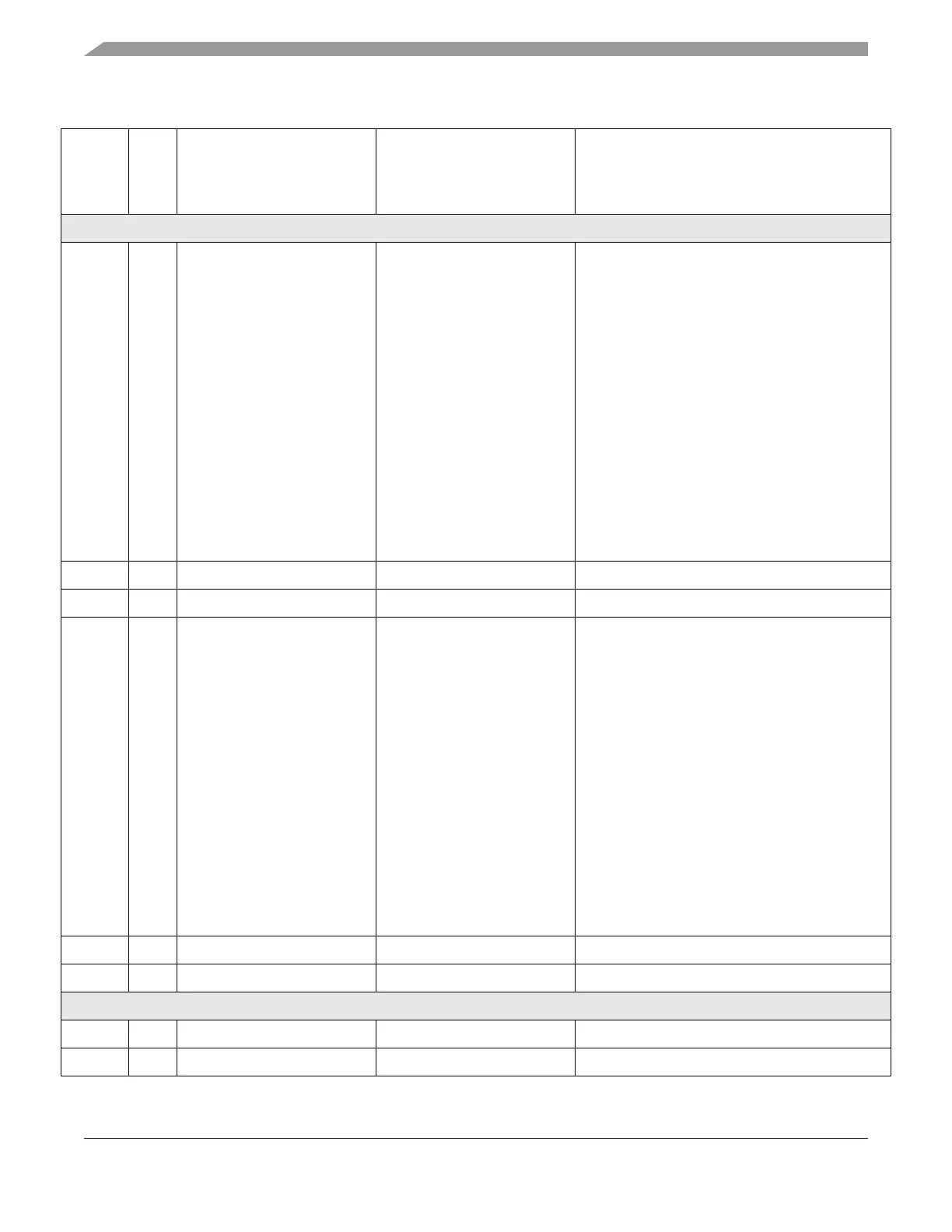

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

10-22 Freescale Semiconductor

eSCI

0x0920 146 ESCIA_SR[TDRE]

ESCIA_SR[TC]

ESCIA_SR[RDRF]

ESCIA_SR[IDLE]

ESCIA_SR[OR]

ESCIA_SR[NF]

ESCIA_SR[FE]

ESCIA_SR[PF]

ESCIA_SR[BERR]

ESCIA_SR[RXRDY]

ESCIA_SR[TXRDY]

ESCIA_SR[LWAKE]

ESCIA_SR[STO]

ESCIA_SR[PBERR]

ESCIA_SR[CERR]

ESCIA_SR[CKERR]

ESCIA_SR[FRC]

ESCIA_SR[OVFL]

ESCIA_SR[TDRE]

ESCIA_SR[TC]

ESCIA_SR[RDRF]

ESCIA_SR[IDLE]

ESCIA_SR[OR]

ESCIA_SR[NF]

ESCIA_SR[FE]

ESCIA_SR[PF]

ESCIA_SR[BERR]

ESCIA_SR[RXRDY]

ESCIA_SR[TXRDY]

ESCIA_SR[LWAKE]

ESCIA_SR[STO]

ESCIA_SR[PBERR]

ESCIA_SR[CERR]

ESCIA_SR[CKERR]

ESCIA_SR[FRC]

ESCIA_SR[OVFL]

Combined Interrupt Requests of ESCI Module A:

Transmit Data Register Empty, Transmit Complete,

Receive Data Register Full, Idle line, Overrun,

Noise Flag, Framing Error Flag, and Parity Error

Flag interrupt requests, SCI Status Register 2 Bit

Error interrupt request, LIN Status Register 1

Receive Data Ready, Transmit Data Ready,

Received LIN Wakeup Signal, Slave TimeOut,

Physical Bus Error, CRC Error, Checksum Error,

Frame Complete interrupts requests, and LIN

Status Register 2 Receive Register Overflow

0x0930 147 Reserved Reserved Reserved

0x0940 148 Reserved Reserved Reserved

0x0950 149 ESCIB_SR[TDRE]

ESCIB_SR[TC]

ESCIB_SR[RDRF]

ESCIB_SR[IDLE]

ESCIB_SR[OR]

ESCIB_SR[NF]

ESCIB_SR[FE]

ESCIB_SR[PF]

ESCIB_SR[BERR]

ESCIB_SR[RXRDY]

ESCIB_SR[TXRDY]

ESCIB_SR[LWAKE]

ESCIB_SR[STO]

ESCIB_SR[PBERR]

ESCIB_SR[CERR]

ESCIB_SR[CKERR]

ESCIB_SR[FRC]

ESCIB_SR[OVFL]

ESCIB_SR[TDRE]

ESCIB_SR[TC]

ESCIB_SR[RDRF]

ESCIB_SR[IDLE]

ESCIB_SR[OR]

ESCIB_SR[NF]

ESCIB_SR[FE]

ESCIB_SR[PF]

ESCIB_SR[BERR]

ESCIB_SR[RXRDY]

ESCIB_SR[TXRDY]

ESCIB_SR[LWAKE]

ESCIB_SR[STO]

ESCIB_SR[PBERR]

ESCIB_SR[CERR]

ESCIB_SR[CKERR]

ESCIB_SR[FRC]

ESCIB_SR[OVFL]

Combined Interrupt Requests of ESCI Module B:

Transmit Data Register Empty, Transmit Complete,

Receive Data Register Full, Idle line, Overrun,

Noise Flag, Framing Error Flag, and Parity Error

Flag interrupt requests, SCI Status Register 2 Bit

Error interrupt request, LIN Status Register 1

Receive Data Ready, Transmit Data Ready,

Received LIN Wakeup Signal, Slave TimeOut,

Physical Bus Error, CRC Error, Checksum Error,

Frame Complete interrupts requests, and LIN

Status Register 2 Receive Register Overflow

0x0960 150 Reserved Reserved Reserved

0x0970 151 Reserved Reserved Reserved

FlexCAN_A and FlexCAN_B

0x0980 152 CANA_ESR[BOFF_INT] CANA_ESR[BOFF_INT] FLEXCAN_A Bus off Interrupt

0x0990 153 CANA_ESR[ERR_INT] CANA_ESR[ERR_INT] FLEXCAN_A Error Interrupt

Table 10-9. INTC: Interrupt Request Sources (Continued)

Hardware

Vector

Mode

Offset

Vector

Source

1

MPC5553

Source

1

MPC5554

Description

Loading...

Loading...