MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 11-21

11.4.1.3 Clock Dividers

Each of the CLKOUT, MCKO, and ENGCLK dividers provides a nominal 50% duty cycle clock to an

output pin. There is no guaranteed phase relationship between CLKOUT, MCKO, and ENGCLK.

ENGCLK is not synchronized to any I/O pins.

11.4.1.3.1 External Bus Clock (CLKOUT)

The external bus clock (CLKOUT) divider can be programmed to divide the system clock by two or four

based on the settings of the EBDF bit field in the SIU external clock control register (SIU_ECCR). The

reset value of the EBDF selects a CLKOUT frequency of one half of the system clock frequency. The EBI

supports gating of the CLKOUT signal when there are no external bus accesses in progress. See the

Chapter 6, “System Integration Unit (SIU)” for more information on CLKOUT.

The hold-time for the external bus pins can be changed by writing to the external bus tap select (EBTS)

bit in the SIU_ECCR. See Chapter 6, “System Integration Unit (SIU)” for more information.

11.4.1.3.2 Nexus Message Clock (MCKO)

The Nexus message clock (MCKO) divider can be programmed to divide the system clock by two, four or

eight based on the MCKO_DIV bit field in the port configuration register (PCR) in the Nexus port

controller (NPC). The reset value of the MCKO_DIV selects an MCKO clock frequency one half of the

system clock frequency. The MCKO divider is configured by writing to the NPC through the JTAG port.

See Chapter 25, “Nexus Development Interface” for more information.

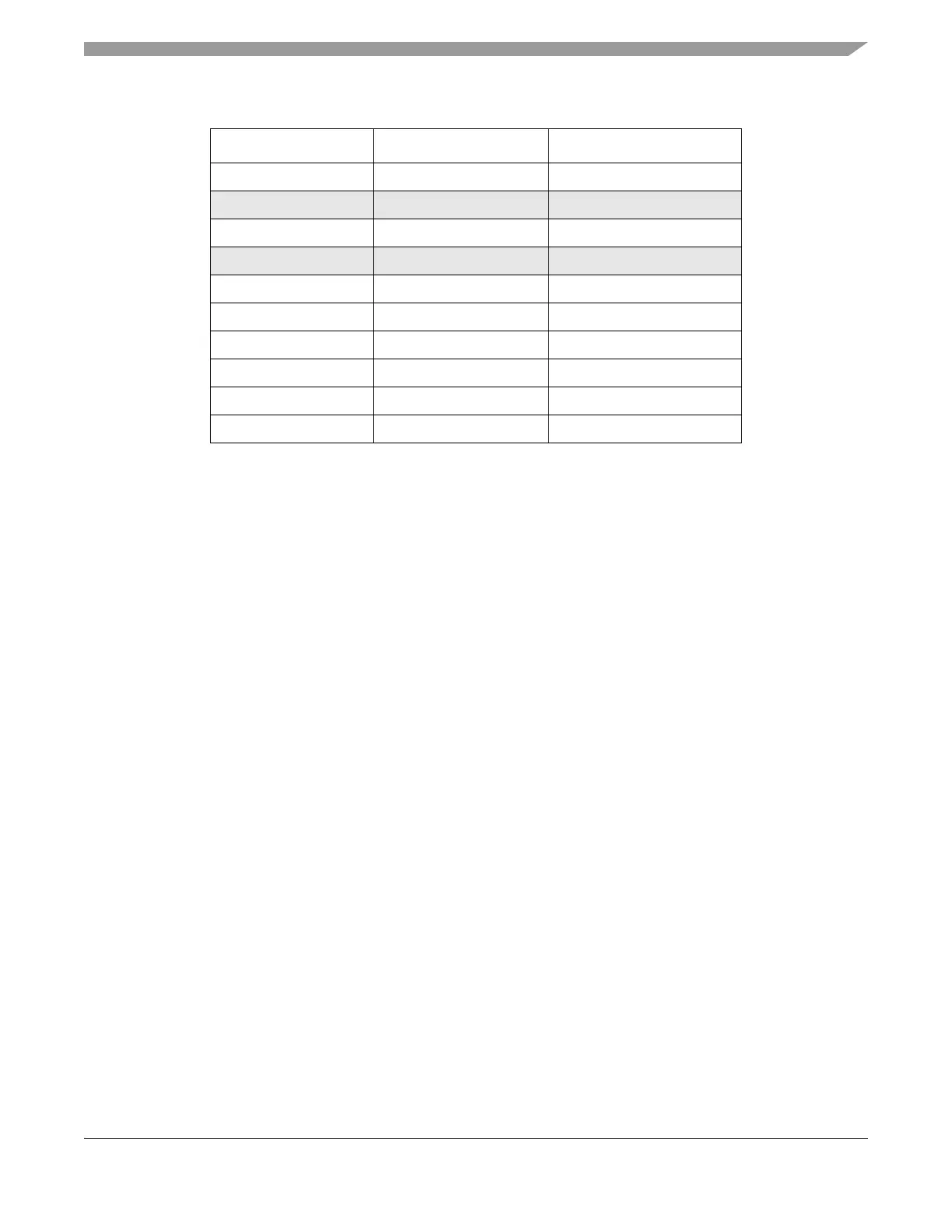

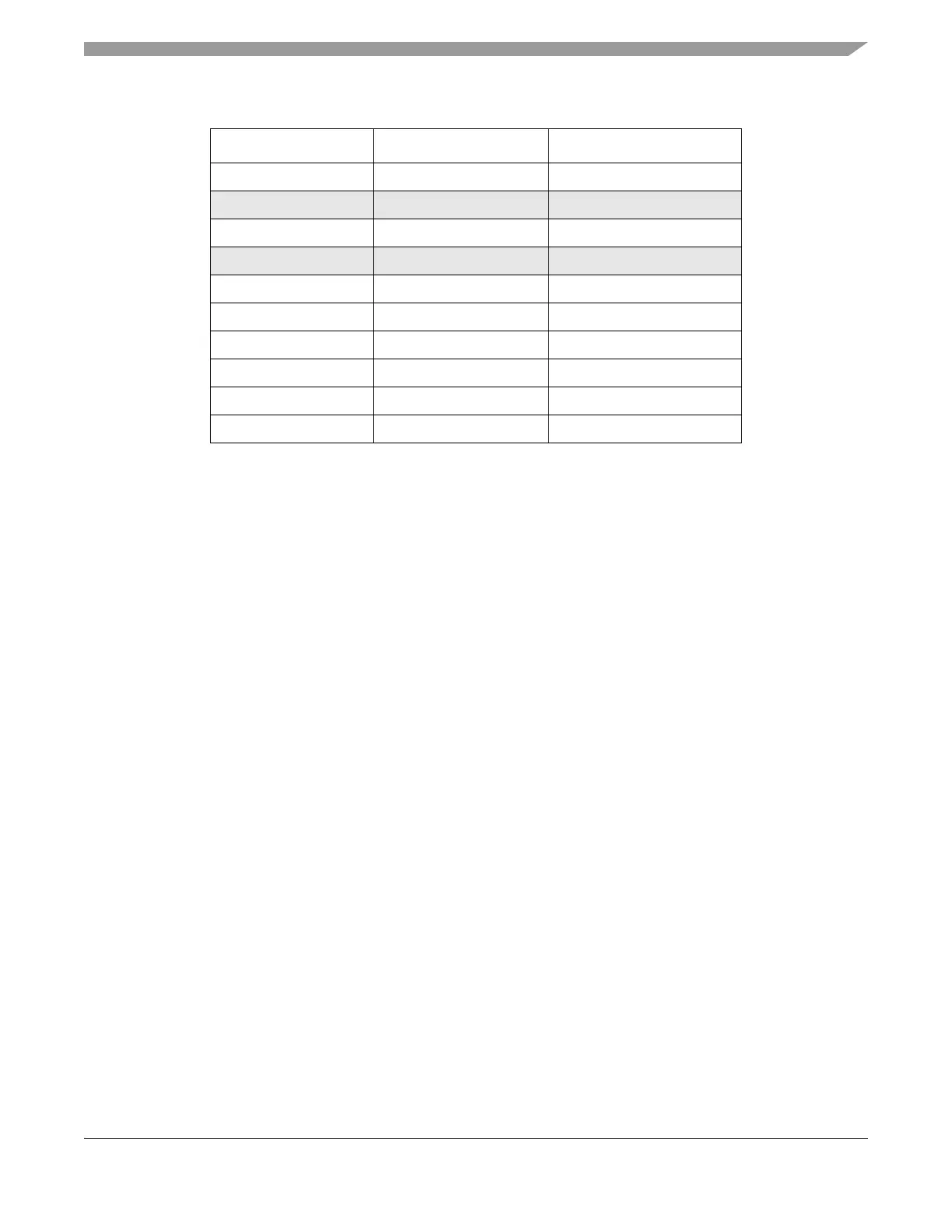

eTPU Engine A ETPUECR_1 MDIS

eTPU Engine B ETPUECR_2 MDIS

FlexCAN A FLEXCAN_A_MCR MDIS

FlexCAN B

1

FLEXCAN_B_MCR MDIS

FlexCAN C FLEXCAN_C_MCR MDIS

EMIOS EMIOS_MCR MDIS

ESCI_A ESCIA_CR2 MDIS

ESCI_B ESCIB_CR2 MDIS

NPC NPC_PCR MCKO_EN, MCKO_GT

2

Flash Array FLASH_MCR STOP

3

1

Shaded areas indicate that module is only offered on the MPC5554, not on the

MPC5553.

2

See Chapter 25, “Nexus Development Interface.”

3

See Chapter 13, “Flash Memory.”

Table 11-7. Software Controlled Power Management/Clock Gating Support (Continued)

Module Name Register Name Bit Names

Loading...

Loading...