MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 13-9

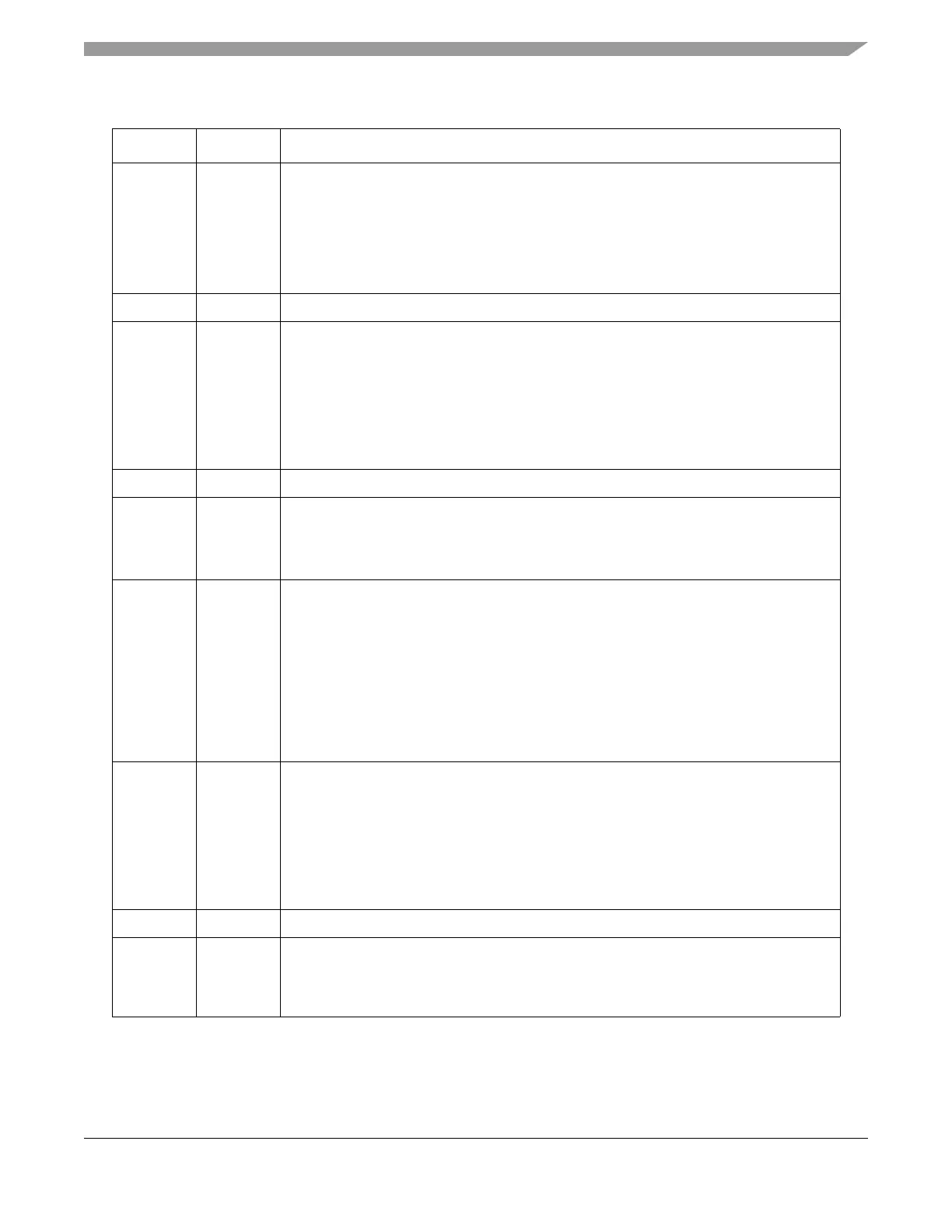

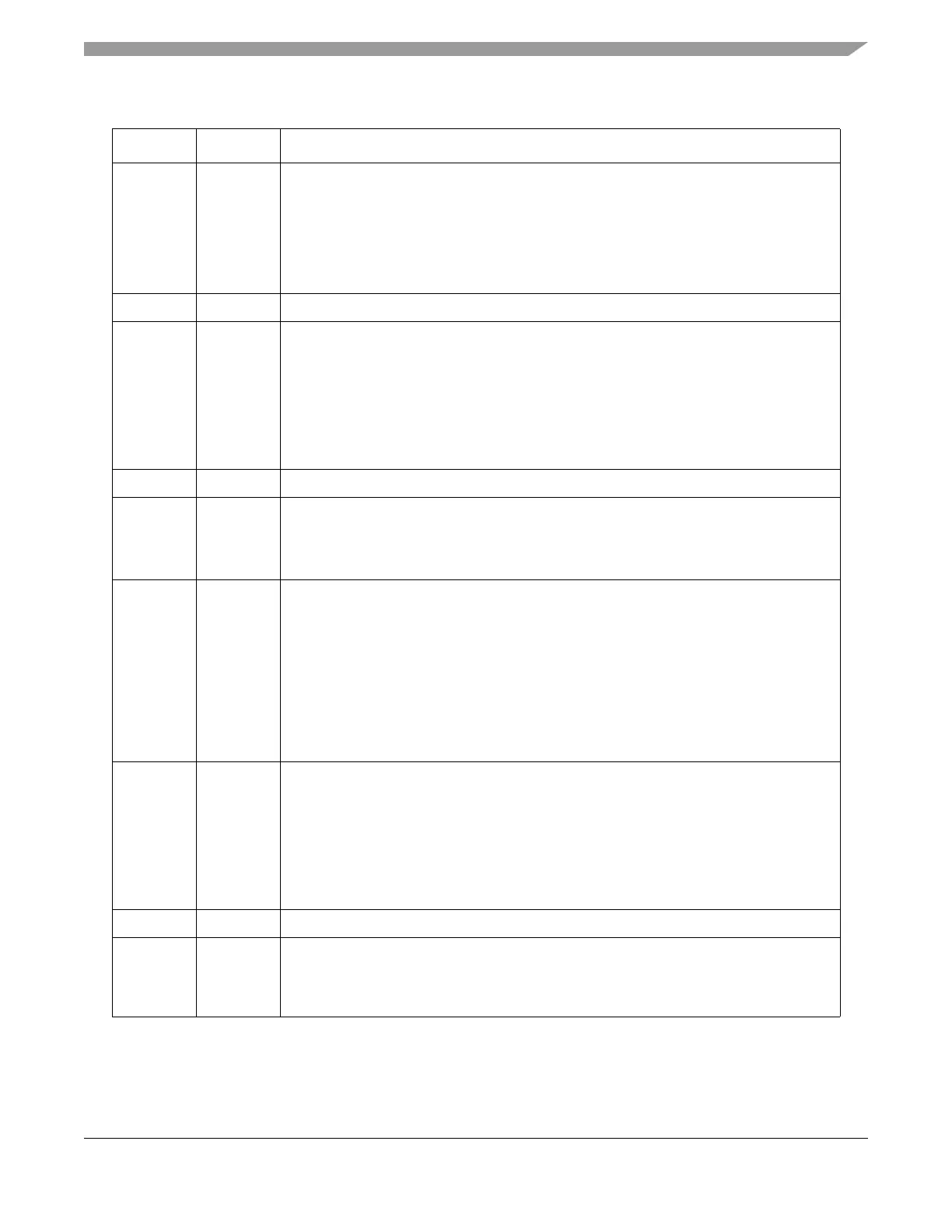

4–7 SIZE

[0:3]

Array space size. Dependent upon the size of the flash module. All possible values of SIZE

and the configuration to which each value corresponds are shown below. SIZE is read

only.

0101 Total array size is 1.5 MB(MPC5553)

0111 Total array size is 2 MB (MPC5554)

8 — Reserved.

9–11 LAS

[2:0]

Low-address space. Corresponds to the configuration of the low-address space. All

possible values of LAS and the configuration to which each value corresponds are shown

below. LAS is read only.

110 The LAS value of 110 provides two 16 KB blocks, two 48 KB blocks,

and two 64 KB blocks. This is the space configuration for both the MPC5553 and the

MPC5554.

12–14 — Reserved.

15 MAS Mid-address space size. Corresponds to the configuration of the mid address space. MAS

is read only. The value of the parameter for this device is shown in bold.

Note: The MAS encoding for the MPC5554 and for the MPC5553 is 0.

0 Two 128 KB blocks are available

16 EER ECC event error. Provides information on previous reads; if a double bit detection occurred,

the EER bit will be set to a 1. This bit must then be cleared, or a reset must occur before

this bit will return to a 0 state. This bit may not be set by the user. In the event of a single

bit detection and correction, this bit will not be set. If EER is not set, or remains 0, this

indicates that all previous reads (from the last reset, or clearing of EER) were correct.

Because this bit is an error flag, it must be cleared to a 0 by writing a 1 to the register

location. A write of 0 will have no effect.

0 Reads are occurring normally.

1 An ECC Error occurred during a previous read.

Note: This bit can be set on speculative prefetches that cause double bit error detection.

17 RWE Read while write event error. Provides information on previous RWW reads. If a read while

write error occurs, this bit will be set to 1. This bit must then be cleared, or a reset must

occur before this bit will return to a 0 state. This bit may not be written to a 1 by the user. If

RWE is not set, or remains 0, this indicates that all previous RWW reads (from the last

reset, or clearing of RWE) were correct. Because this bit is an error flag, it must be cleared

to a 0 by writing a 1 to the register location. A write of 0 will have no effect.

0 Reads are occurring normally.

1 A read while write error occurred during a previous read.

18–19 — Reserved.

20 PEAS Program/erase access space. Indicates which space is valid for program and erase

operations, either main array space or shadow space. PEAS is read only.

0 Shadow address space is disabled for program/erase and main address space enabled

1 Shadow address space is enabled for program/erase and main address space disabled.

Table 13-6. FLASH_MCR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...