MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

14-50 Freescale Semiconductor

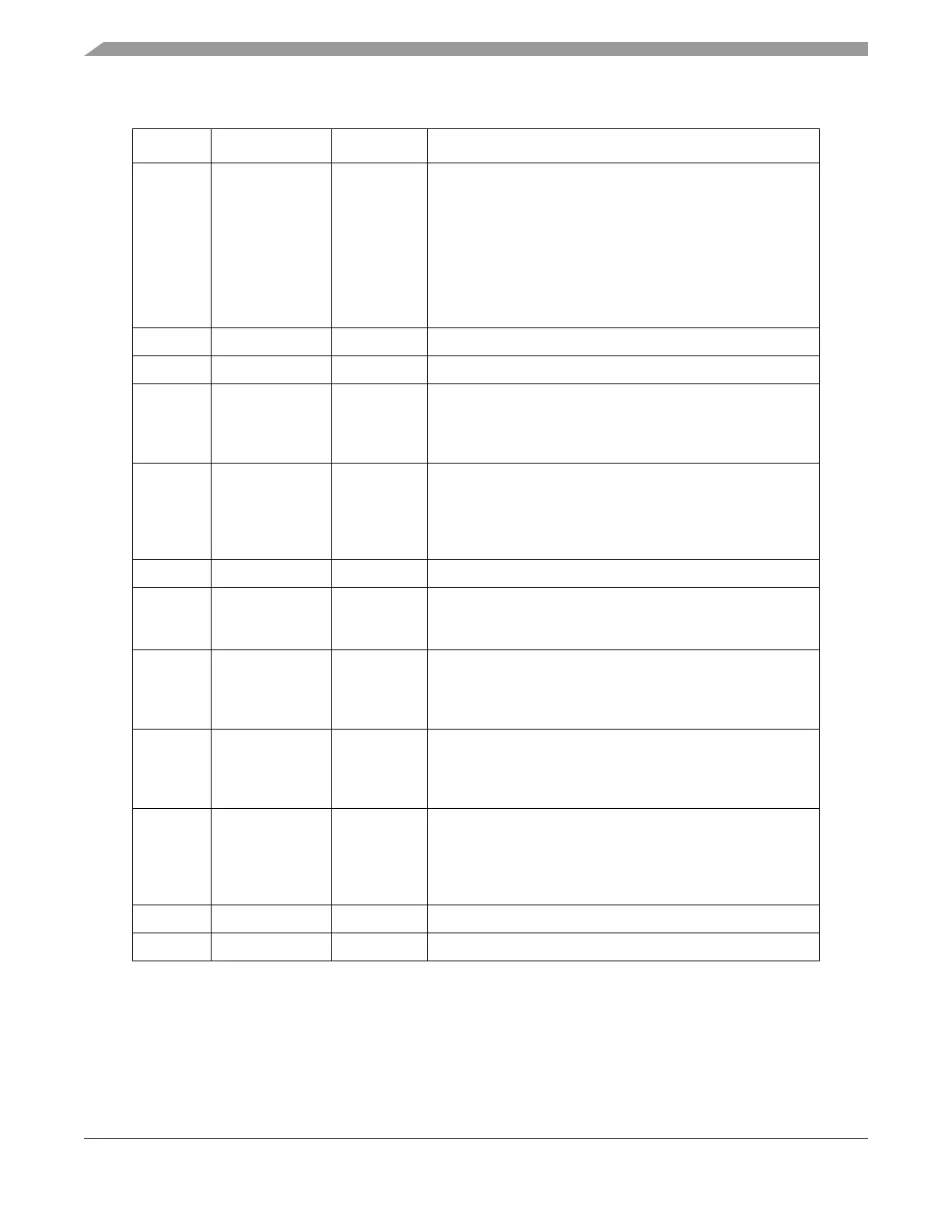

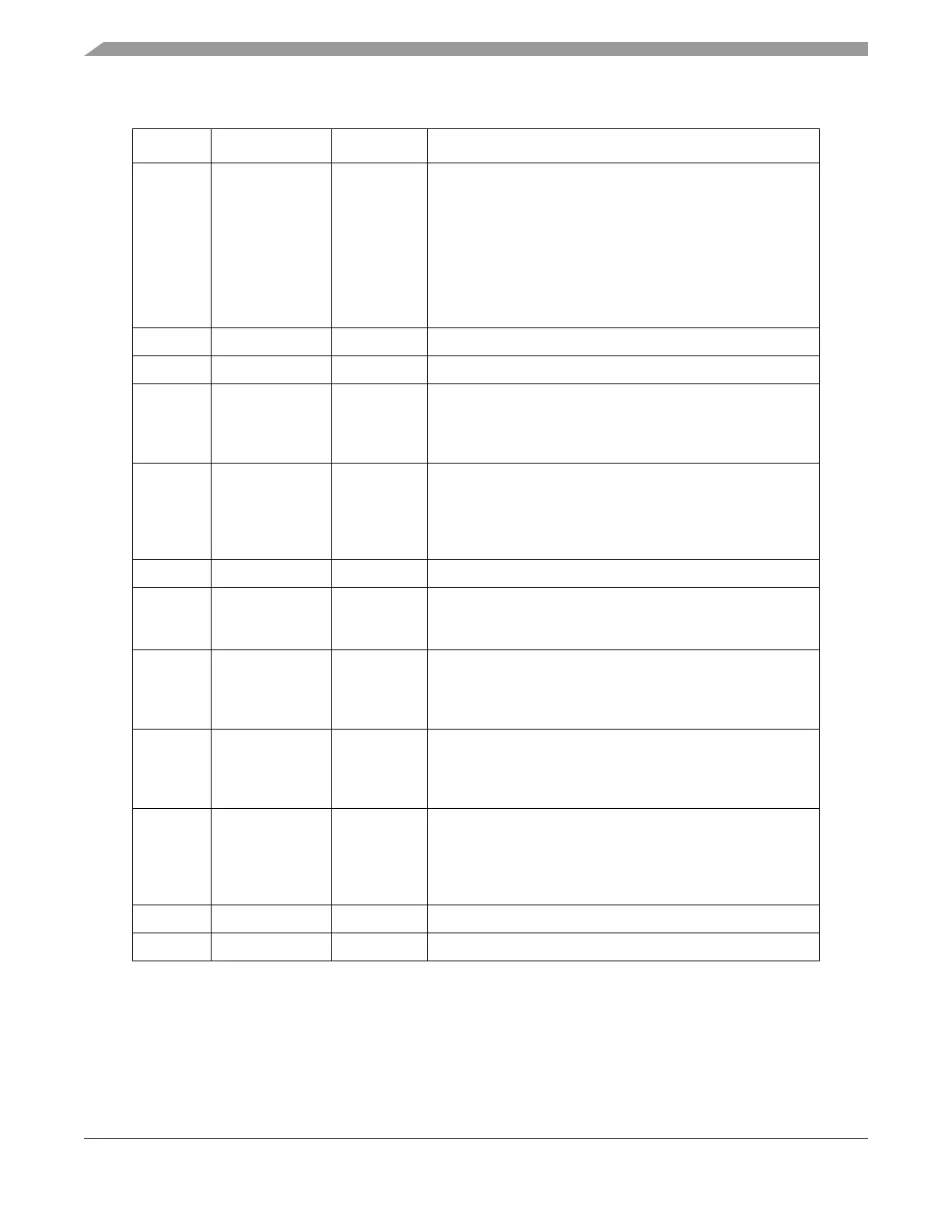

Offset + 0 Bit 7 M Miss. Written by the FEC. This bit is set by the FEC for frames

that were accepted in promiscuous mode, but were flagged as

a “miss” by the internal address recognition. Thus, while in

promiscuous mode, the user can use the M-bit to quickly

determine whether the frame was destined to this station. This

bit is valid only if the L-bit is set and the PROM bit is set.

0 The frame was received because of an address recognition

hit.

1 The frame was received because of promiscuous mode.

Offset + 0 Bit 8 BC Will be set if the DA is broadcast (FF-FF-FF-FF-FF-FF).

Offset + 0 Bit 9 MC Will be set if the DA is multicast and not BC.

Offset + 0 Bit 10 LG Rx frame length violation. Written by the FEC. A frame length

greater than RCR[MAX_FL] was recognized. This bit is valid

only if the L-bit is set. The receive data is not altered in any way

unless the length exceeds 2047 bytes.

Offset + 0 Bit 11 NO Receive non-octet aligned frame. Written by the FEC. A frame

that contained a number of bits not divisible by 8 was received,

and the CRC check that occurred at the preceding byte

boundary generated an error. This bit is valid only if the L-bit is

set. If this bit is set the CR bit will not be set.

Offset + 0 Bit 12 — Reserved.

Offset + 0 Bit 13 CR Receive CRC error. Written by the FEC. This frame contains a

CRC error and is an integral number of octets in length. This bit

is valid only if the L-bit is set.

Offset + 0 Bit 14 OV Overrun. Written by the FEC. A receive FIFO overrun occurred

during frame reception. If this bit is set, the other status bits, M,

LG, NO, CR, and CL lose their normal meaning and will be

zero. This bit is valid only if the L-bit is set.

Offset + 0 Bit 15 TR Will be set if the receive frame is truncated (frame length >

2047 bytes). If the TR bit is set the frame should be discarded

and the other error bits should be ignored as they may be

incorrect.

Offset + 2 Bits [0:15] Data Length Data length. Written by the FEC. Data length is the number of

8-bit data groups (octets) written by the FEC into this BD’s data

buffer if L = 0 (the value will be equal to EMRBR), or the length

of the frame including CRC if L = 1. It is written by the FEC after

as the BD is closed.

0ffset + 4 Bits [0:15] A[0:15]] RX data buffer pointer, bits [0:15]

1

Offset + 6 Bits [0:15] A[16:31] RX data buffer pointer, bits [16:31]

1

The receive buffer pointer, which contains the address of the associated data buffer, must always be evenly

divisible by 16. The buffer must reside in memory external to the FEC. This value is never modified by the

Ethernet controller.

Table 14-37. Receive Buffer Descriptor Field Definitions (Continued)

Halfword Location Field Name Description

Loading...

Loading...