MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 17-21

17.3.1.8 eMIOS Channel Status Register (EMIOS_CSRn)

EMIOS_CSRn reflects the status of the UC input/output signals and the overflow condition of the internal

counter, as well as the occurrence of a trigger event.

1011110 Center aligned output pulse width modulation, buffered

(FLAG set on both edges, trailing edge dead-time)

1011111 Center aligned output pulse width modulation, buffered

(FLAG set on both edges, leading edge dead-time)

1100000 Output pulse width modulation, buffered

(FLAG set on second match)

1100001 Reserved

1100010 Output pulse width modulation, buffered

(FLAG set on both matches)

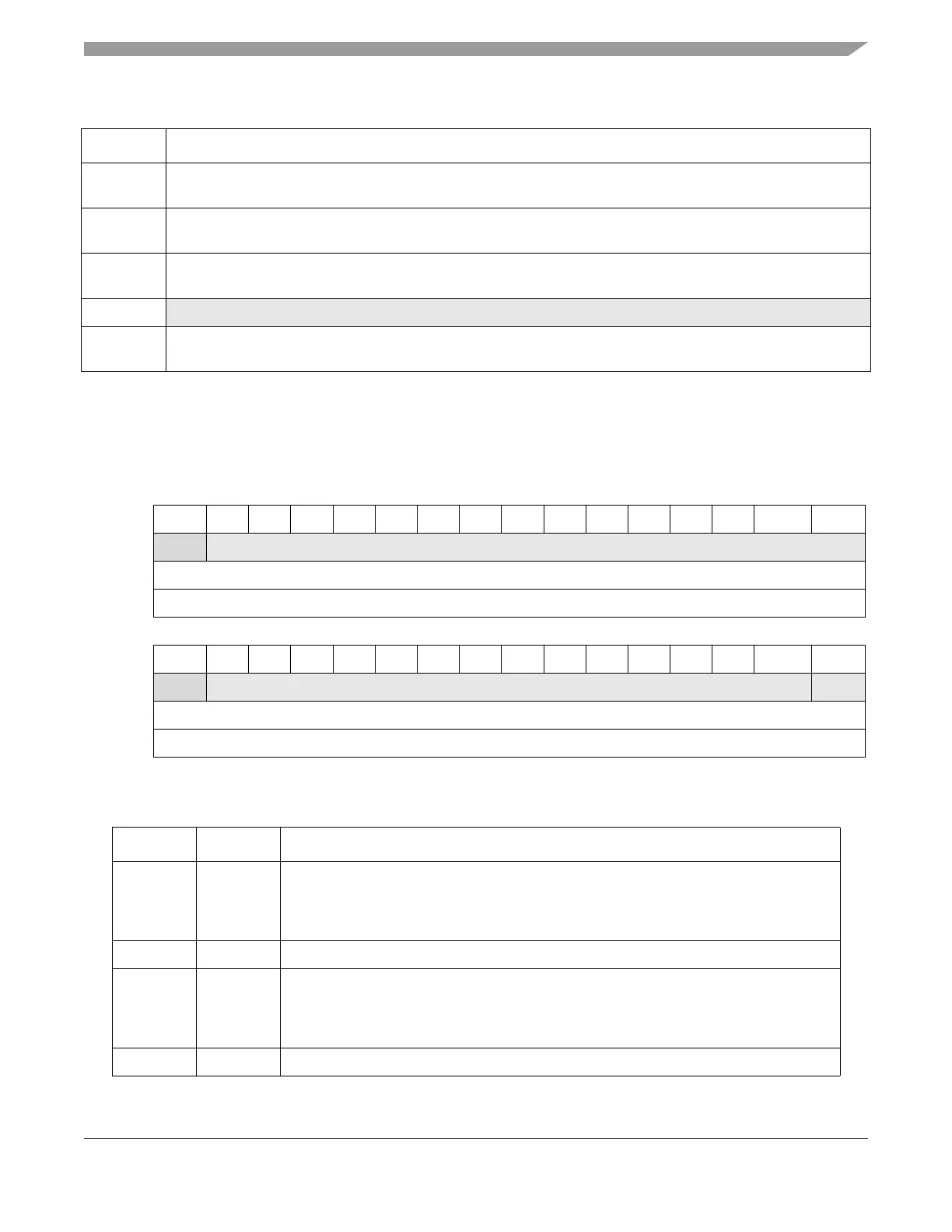

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

ROVR0000000000000 0 0

W w1c

Reset0 0000000000000 0 0

Reg Addr UCn Base + 0x0010

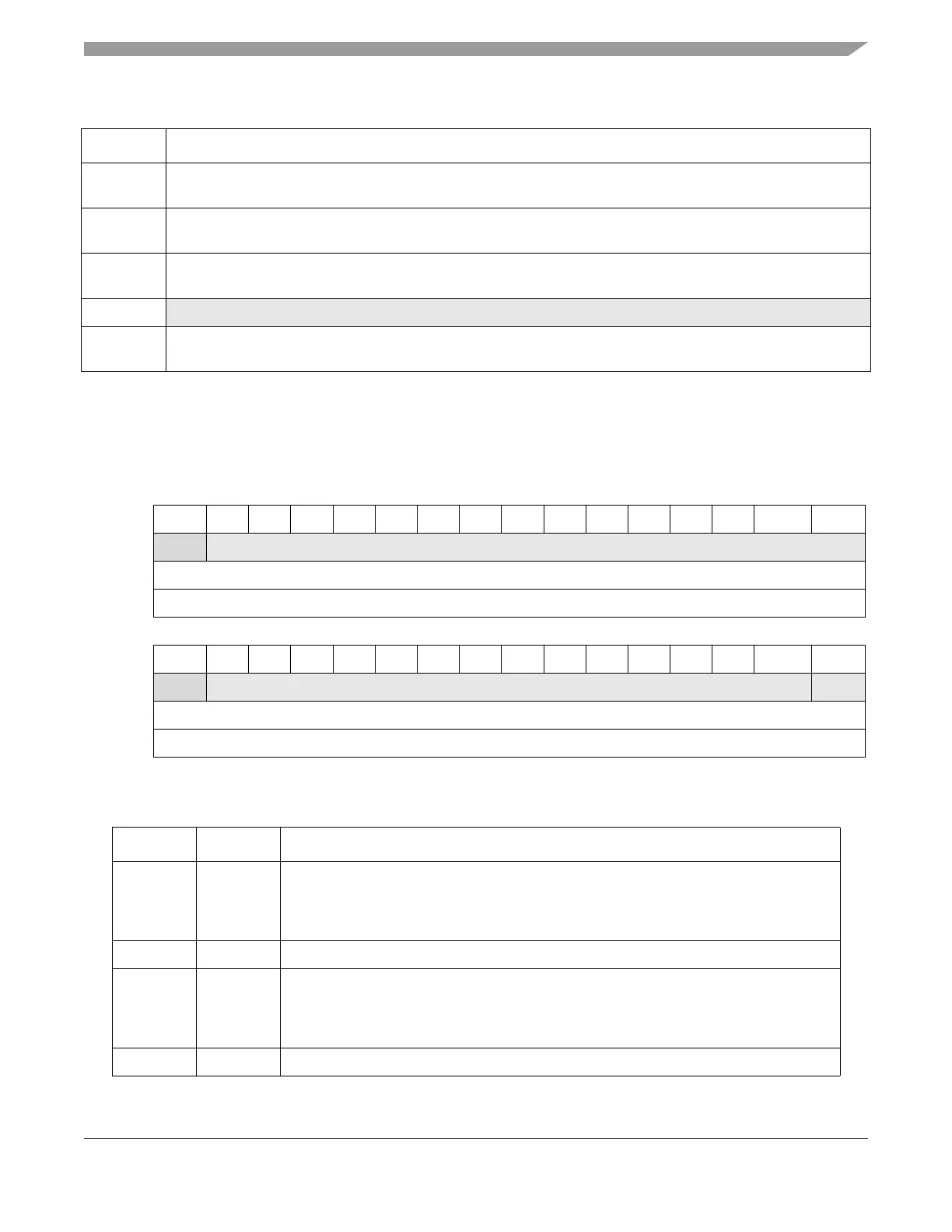

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

ROVFL000000000000UCINUCOUTFLAG

W w1c w1c

Reset0 0000000000000 0 0

Reg Addr UCn Base + 0x0010

Figure 17-9. eMIOS Channel Status Register (EMIOS_CSRn)

Table 17-12. EMIOS_CSRn Field Descriptions

Bits Name Description

0 OVR Overrun. Indicates that FLAG generation occurred when the FLAG bit was already set.

This bit can be cleared by writing a 1 to it or by clearing the FLAG bit.

0 Overrun has not occurred

1 Overrun has occurred

1–15 — Reserved.

16 OVFL Overflow. Indicates that an overflow has occurred in the internal counter. OVFL is cleared

by writing a 1 to it.

0 No overflow

1 An overflow had occurred

17–28 — Reserved.

Table 17-11. Unified Channel MODE Bits (Sheet 4 of 4)

MODE0:6] Unified Channel Mode of Operation

Loading...

Loading...