MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

19-38 Freescale Semiconductor

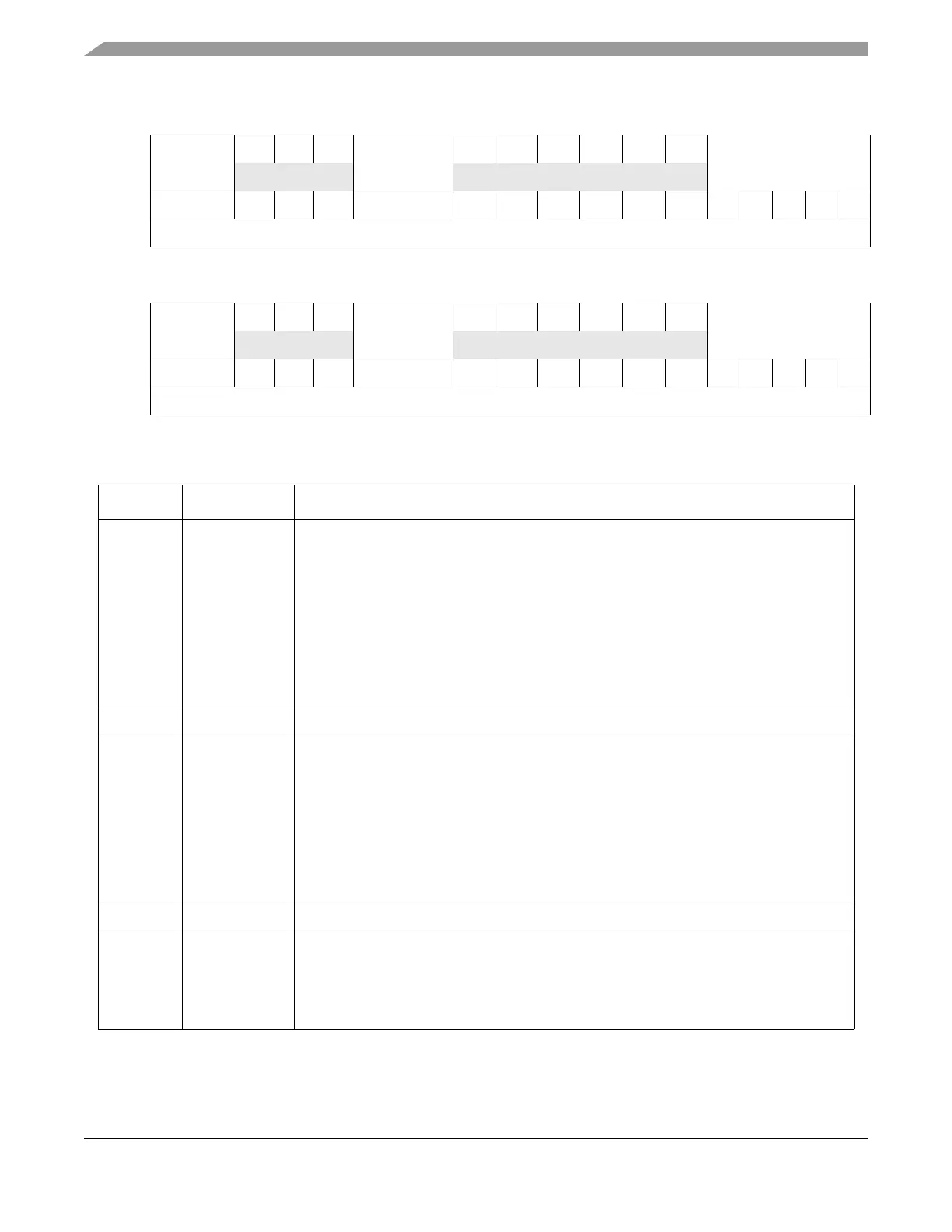

0 123 4 56789101112131415

RADC0_EN000ADC0_EMUX000000 ADC0_CLK_PS

W

Reset 0 000 0 00000011111

Reg Addr 0x01

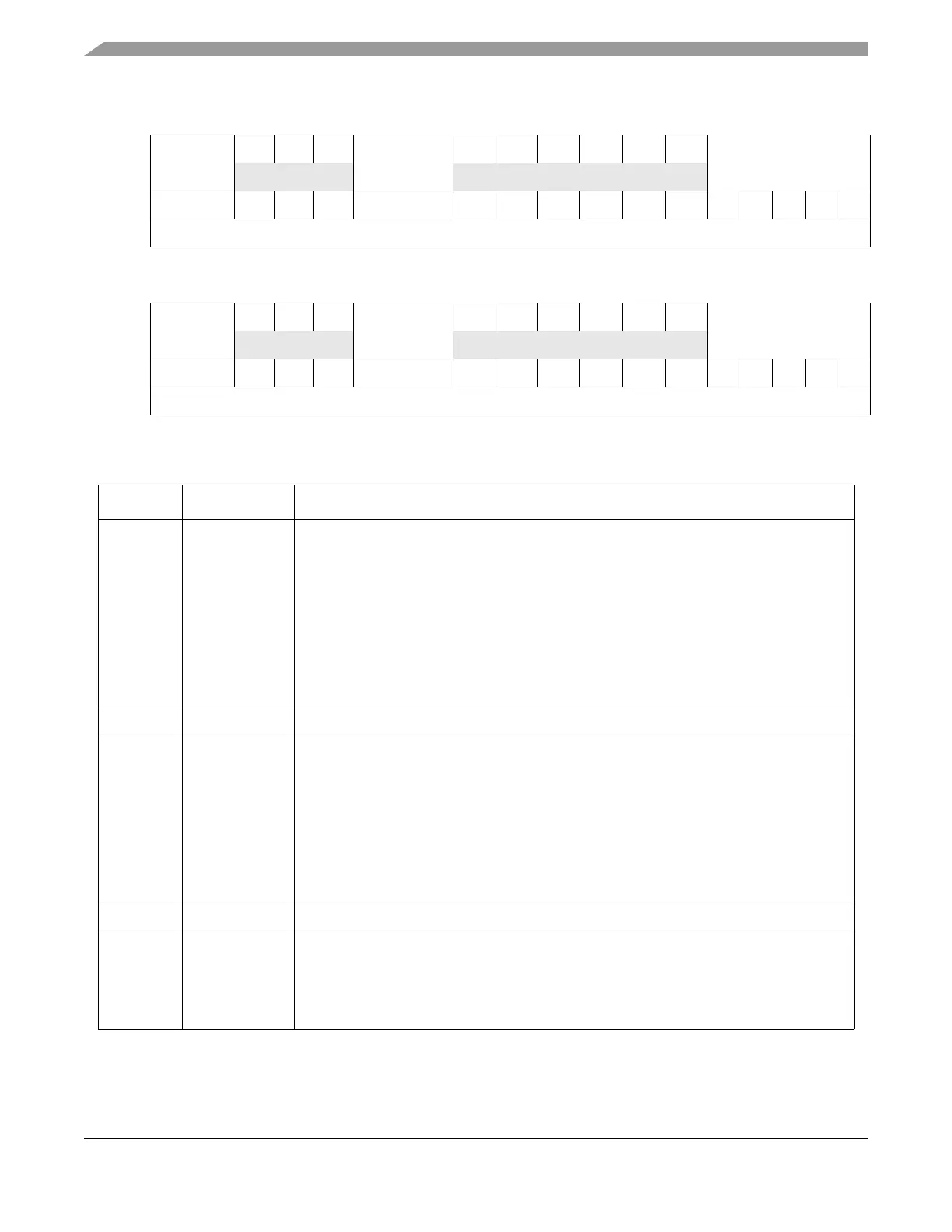

0 123 4 56789101112131415

RADC1_EN000ADC1_EMUX000000 ADC1_CLK_PS

W

Reset 0 000 0 00000011111

Reg Addr 0x01

Figure 19-19. ADCn Control Registers (ADC0_CR and ADC1_CR)

Table 19-27. ADCn_CR Field Descriptions

Bits Name Description

0ADCn_EN

ADCn enable. Enables ADCn to perform A/D conversions. Refer to Section 19.4.5.1,

“Enabling and Disabling the on-chip ADCs,” for details.

0 ADC is disabled. Clock supply to ADC0/1 is stopped.

1 ADC is enabled and ready to perform A/D conversions.

Note: The bias generator circuit inside the ADC ceases functioning when both ADC0_EN

and ADC1_EN bits are negated.

Note: Conversion commands sent to a disabled ADC are ignored by the ADC control

hardware.

Note: When the ADCn_EN status is changed from asserted to negated, the ADC clock

will not stop until it reaches its low phase.

1–3 — Reserved.

4ADCn_EMUX ADCn external multiplexer enable. When ADCn_EMUX is asserted, the MA pins will output

digital values according to the number of the external channel being converted for selecting

external multiplexer inputs. Refer to Section 19.4.6, “Internal/External Multiplexing,” for a

detailed description about how ADCn_EMUX affects channel number decoding.

0 External multiplexer disabled; no external multiplexer channels can be selected.

1 External multiplexer enabled; external multiplexer channels can be selected.

Note: Both ADCn_EMUX bits must not be asserted at the same time.

Note: The ADCn_EMUX bit must only be written when the ADCn_EN bit is negated.

ADCn_EMUX can be set during the same write cycle used to set ADCn_EN.

5–10 — Reserved.

11–15 ADCn_CLK_PS

[0:4]

ADCn clock prescaler. The ADCn_CLK_PS field controls the system clock divide factor for

the ADCn clock as in Table 19-28. See Section 19.4.5.2, “ADC Clock and Conversion

Speed,” for details about how to set ADC0/1_CLK_PS.

The ADCn_CLK_PS field must only be written when the ADCn_EN bit is negated. This field

can be configured during the same write cycle used to set ADCn_EN.

Loading...

Loading...