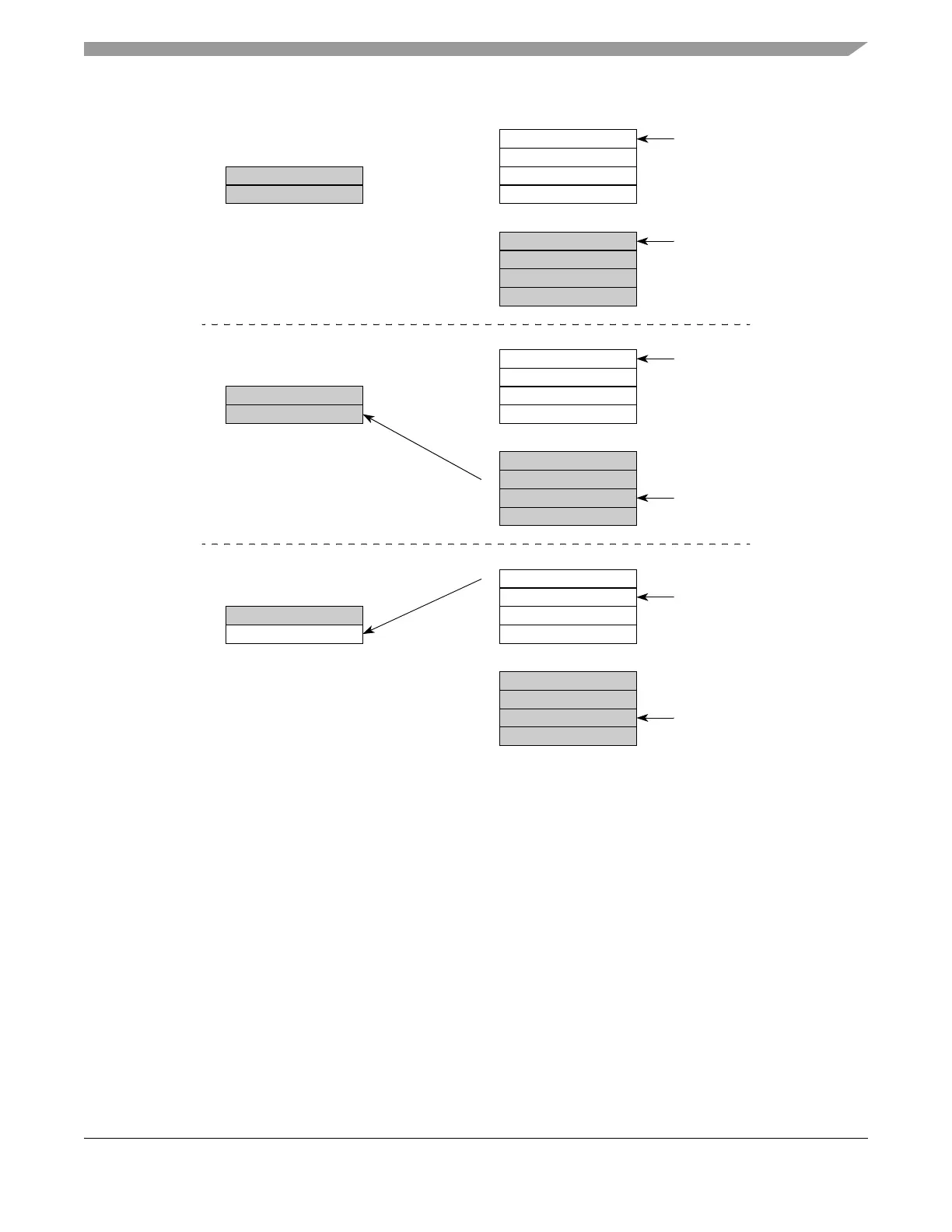

CFIFO5

CF5_ADC1_CM33

CF5_ADC1_CM2

2

CF5_ADC1_CM1

1

CF5_ADC1_CM0

0 TNXTPTR*

ADC1**

Empty1

Empty

0

CFIFO0 and CFIFO5 both have

** ADC command buffer can hold 2 entries.

CFIFO0

CF0_ADC1_CM33

CF0_ADC1_CM2

2

CF0_ADC1_CM1

1

CF0_ADC1_CM0

0 TNXTPTR*

commands to be sent to ADC1, and both

are not triggered.

(a)

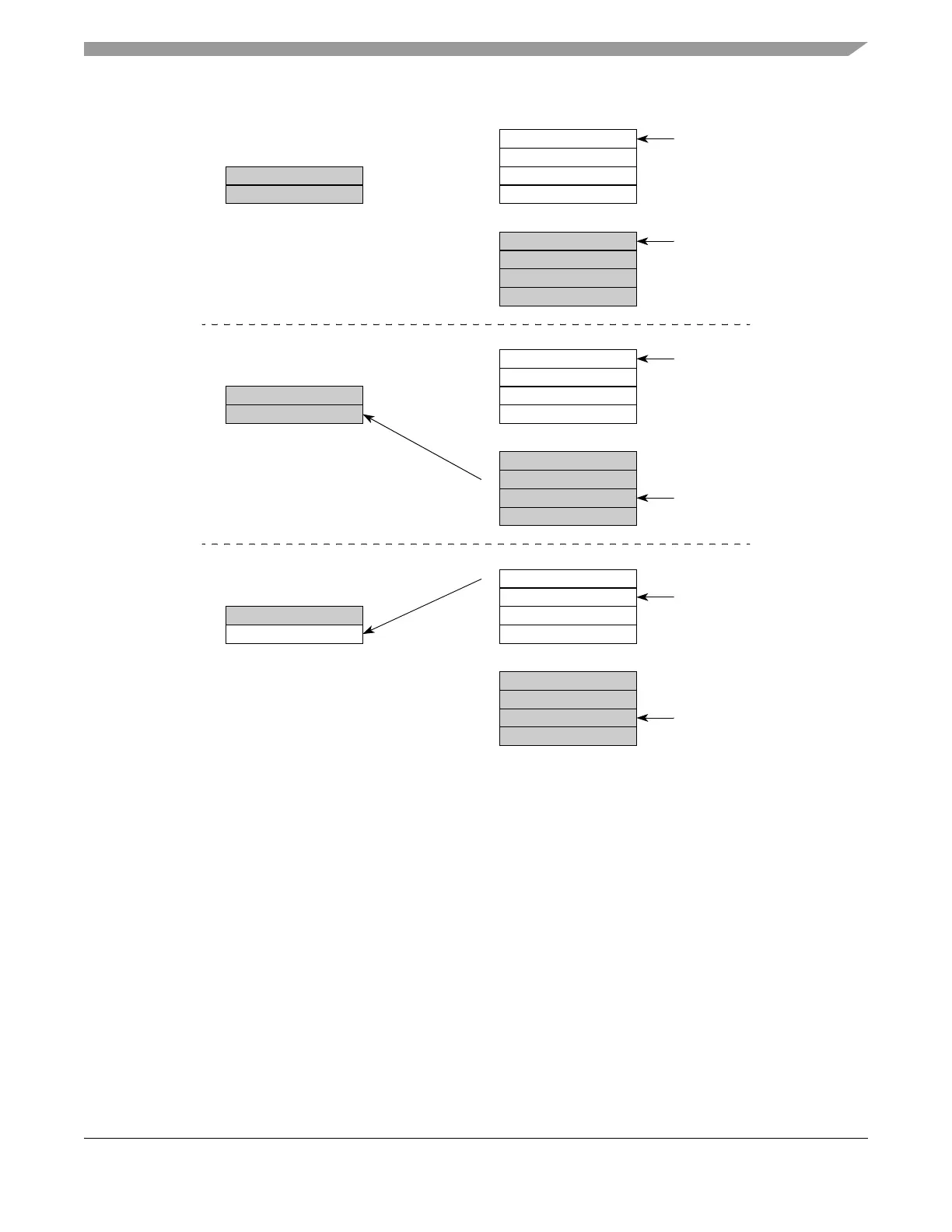

CFIFO5

CF5_ADC1_CM33

CF5_ADC1_CM2

2

Sent

1

Sent

0

TNXTPTR*

ADC1

CF5_ADC1_CM11

CF5_ADC1_CM0

0

CFIFO5 becomes triggered and transfers

CFIFO0

CF0_ADC1_CM33

CF0_ADC1_CM2

2

CF0_ADC1_CM1

1

CF0_ADC1_CM0

0 TNXTPTR*

two commands to ADC1.

(b)

CFIFO5

CF5_ADC1_CM33

CF5_ADC1_CM2

2

Sent

1

Sent

0

TNXTPTR*

ADC1

CF0_ADC1_CM01

CF5_ADC1_CM1

0

CFIFO0 becomes triggered and transfers

CFIFO0

CF0_ADC1_CM33

CF0_ADC1_CM2

2

CF0_ADC1_CM1

1

Sent

0

TNXTPTR*

a command to ADC1. The sequence sent

through CFIFO5 becomes non-coherent.

(c)

TNXTPTR – Transfer Next Data Pointer.

CF

x

_ADCa_CM

n

– Command

n

in CFIFO

x

bound for ADCa.

*

Loading...

Loading...