MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

19-82 Freescale Semiconductor

RFIFO. Using POPNXTPTR and RFCTR, the absolute addresses for pop next data pointer and receive

next data pointer can be calculated using the following formulas:

Pop Next Data Pointer Address= RFIFOn_BASE_ADDRESS + POPNXTPTRn*4

Receive Next Data Pointer Address = RFIFOn_BASE_ADDRESS +

[(POPNXTPTRn + RFCTRn) mod RFIFO_DEPTH] * 4

where

• a mod b returns the remainder of the division of a by b.

• RFIFOn_BASE_ADDRESS is the smallest memory mapped address allocated to an RFIFOn

entry.

• RFIFO_DEPTH is the number of entries contained in a RFIFO - four in this implementation.

When a new message arrives and RFIFOn is not full, the eQADC copies its contents into the entry pointed

by receive next data pointer. The RFIFO counter EQADC_FISRn[RFCTRn] (see Section 19.3.2.8) is

incremented by 1, and the receive next data pointer n is also incremented by 1 (or wrapped around) to point

to the next empty entry in RFIFOn. However, if the RFIFOn is full, the eQADC sets the

EQADC_FISRn[RFOF] (see Section 19.3.2.8). The RFIFOn will not overwrite the older data in the

RFIFO, the new data will be ignored, and the receive next data pointer n is not incremented or wrapped

around. RFIFOn is full when the receive next data pointer n equals the pop next data pointer n and

RFCTRn is not 0. RFIFOn is empty when the receive next data pointer n equals the pop next data pointer

n and RFCTRn is 0.

When the eQADC RFIFO pop register n is read and the RFIFOn is not empty, the RFIFO counter RFCTRn

is decremented by 1, and the pop next data pointer is incremented by 1 (or wrapped around) to point to the

next RFIFO entry.

When the eQADC RFIFO pop register n is read and RFIFOn is empty, eQADC will not decrement the

counter value and the pop next data pointer n will not be updated. The read value will be undefined.

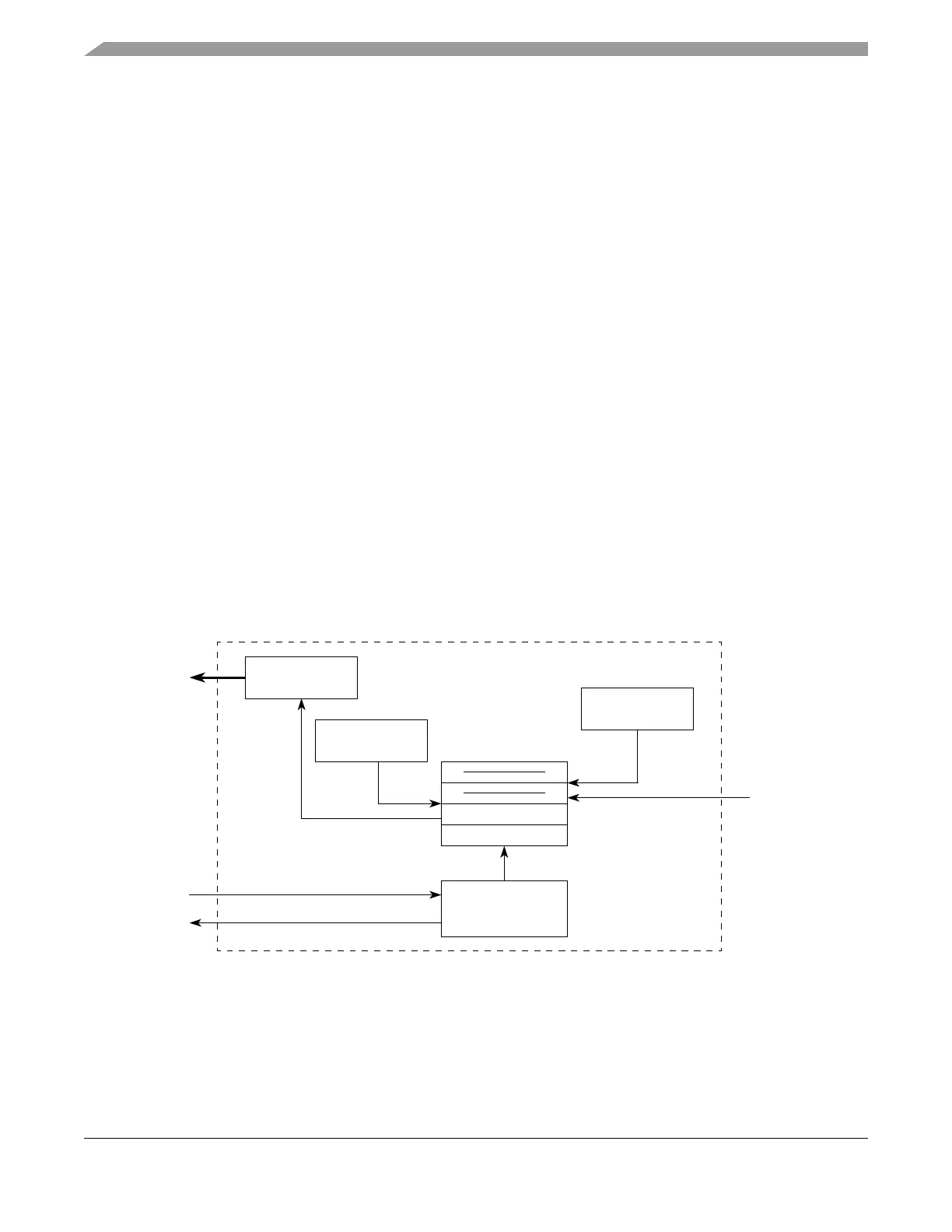

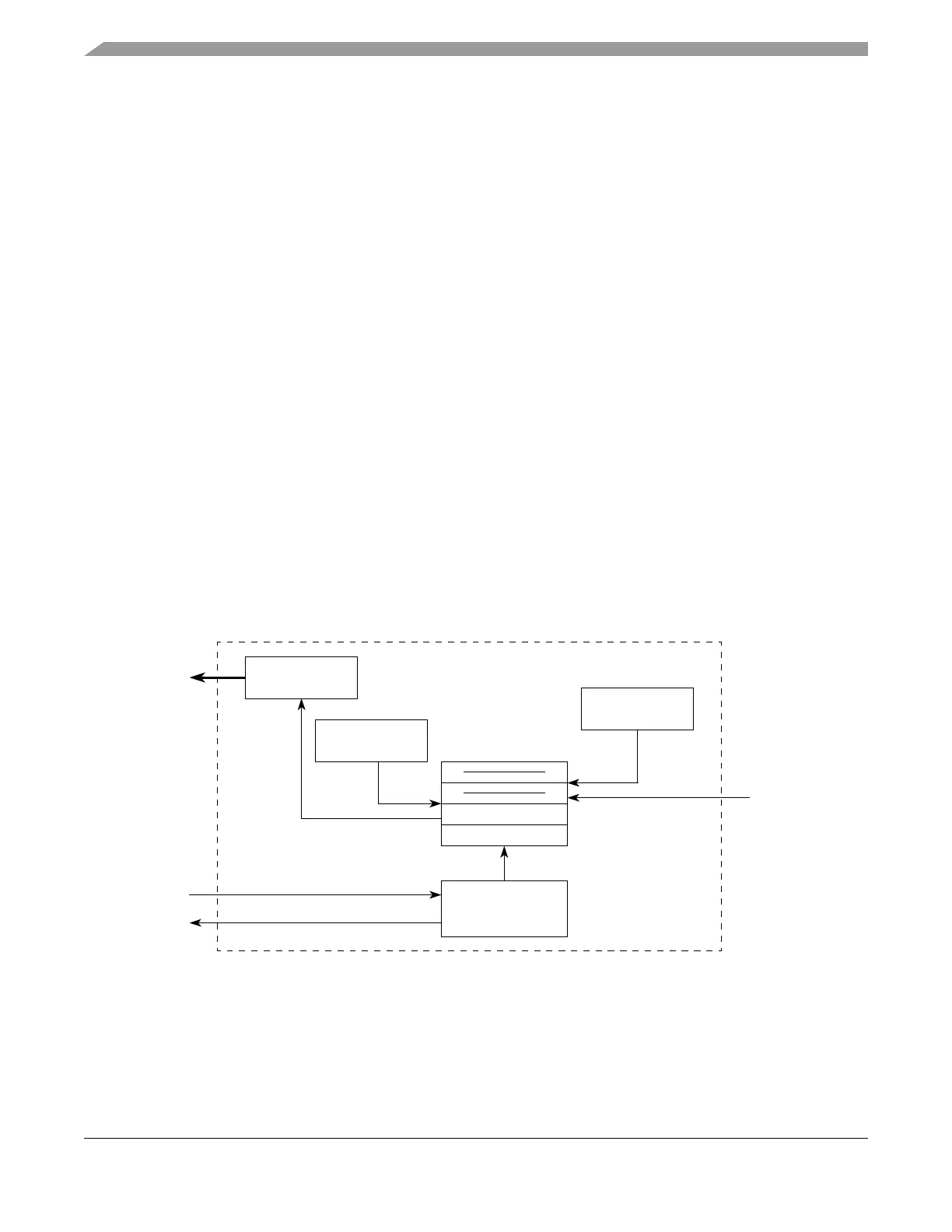

Figure 19-46. RFIFO Diagram

The detailed behavior of the pop next data pointer and receive next data pointer is described in the example

shown in Figure 19-47 where an RFIFO with 16 entries is shown for clarity of explanation, the actual

Pop Next

Data Entry 1

Data Entry 2

Control Signals

RFIFO

Counter Control

Logic

Data Pointer *

Receive Next

Data Pointer *

Data from

External

Device or

from

On-Chip

Read

from Bus

Interface

by CPU

or DMA

DMA Done

Interrupt/DMA Request

All RFIFO entries are memory mapped and the entries addressed by these pointers

can have their absolute addresses calculated using POPNXTPTR and RFCTR.

*

RFIFO

Pop Register

ADCs

Loading...

Loading...