MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 20-23

20.3.2.6 DSPI PUSH TX FIFO Register (DSPIx_PUSHR)

The DSPIx_PUSHR provides a means to write to the TX FIFO. Data written to this register is transferred

to the TX FIFO. See Section 20.4.3.4, “Transmit First In First Out (TX FIFO) Buffering Mechanism,” for

more information. Write accesses of 8- or 16-bits to the DSPIx_PUSHR will transfer 32 bits to the TX

FIFO.

NOTE

TXDATA is used in master and slave modes.

12 RFOF_RE Receive FIFO overflow request enable. Enables the RFOF flag in the DSPIx_SR to

generate an interrupt requests.

0 RFOF interrupt requests are disabled

1 RFOF interrupt requests are enabled

13 — Reserved.

14 RFDF_RE Receive FIFO drain request enable. Enables the RFDF flag in the DSPIx_SR to generate

a request. The RFDF_DIRS bit selects between generating an interrupt request or a DMA

request.

0 RFDF interrupt requests or DMA requests are disabled

1 RFDF interrupt requests or DMA requests are enabled

15 RFDF_DIRS Receive FIFO drain DMA or interrupt request select. Selects between generating a DMA

request or an interrupt request. When the RFDF flag bit in the DSPIx_SR is set, and the

RFDF_RE bit in the DSPIx_RSER is set, the RFDF_DIRS bit selects between generating

an interrupt request or a DMA request.

0 Interrupt request will be generated

1 DMA request will be generated

16–31 — Reserved.

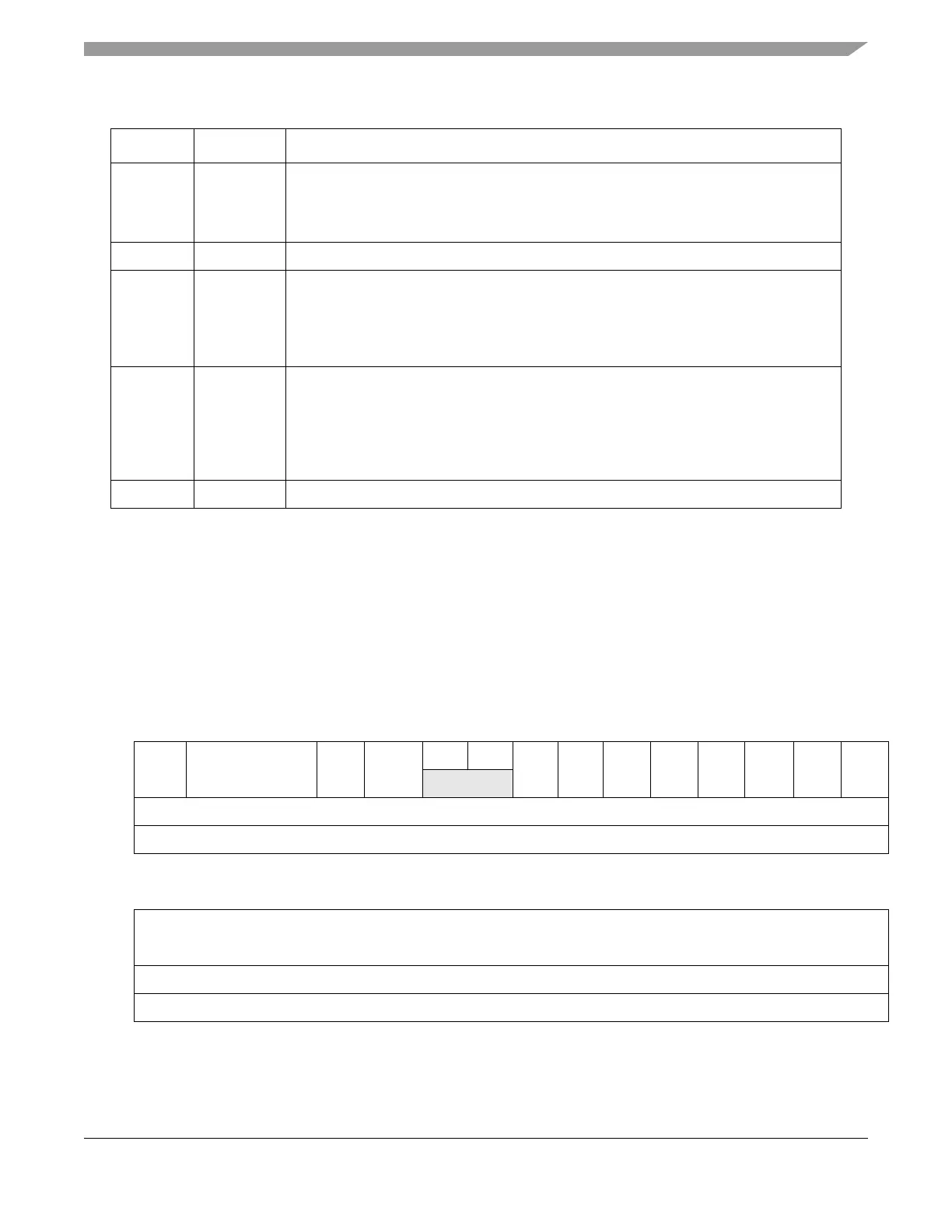

0 1 234 5 6789101112131415

RCONT CTAS EOQCTCNT0000PCS5PCS4PCS3PCS2PCS1PCS0

W

Reset0 0000 0 000000 0 0 0 0

Reg Addr Base + 0x0034

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RTXDATA

W

Reset0 0000 0 000000 0 0 0 0

Reg Addr Base + 0x0034

Figure 20-8. DSPI PUSH TX FIFO Register (DSPIx_PUSHR)

Table 20-7. DSPIx_RSER Field Descriptions

Bits Name Description

Loading...

Loading...