MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 20-25

20.3.2.7 DSPI POP RX FIFO Register (DSPIx_POPR)

The DSPIx_POPR provides a means to read the RX FIFO. See Section 20.4.3.5, “Receive First In First

Out (RX FIFO) Buffering Mechanism” for a description of the RX FIFO operations. Eight or sixteen bit

read accesses to the DSPIx_POPR will read from the RX FIFO and update the counter and pointer.

NOTE

The DSPIx_POPR must not be read speculatively. For future compatibility,

the TLB entry covering the DSPIx_POPR must be configured to be guarded.

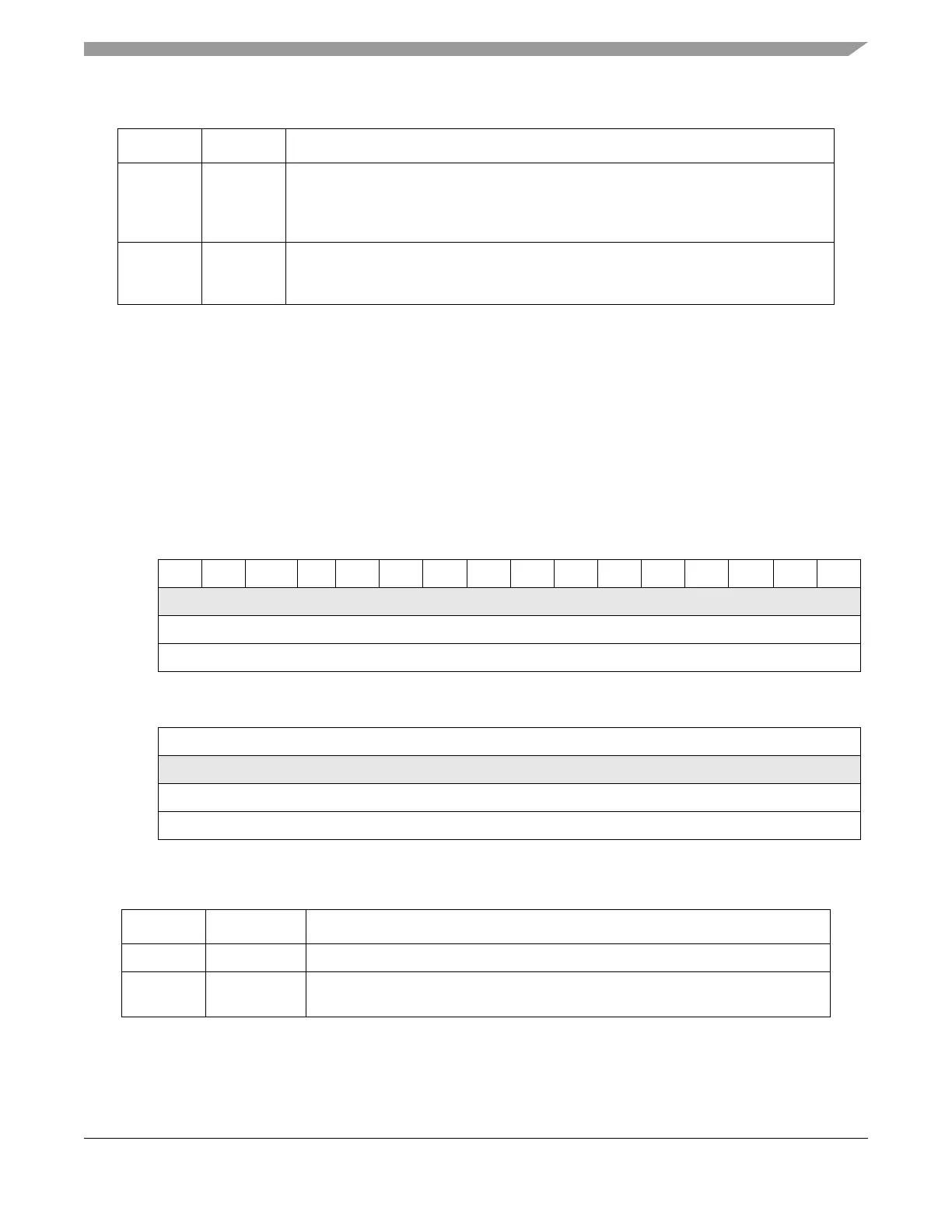

10–15 PCSn Peripheral chip select n. Selects which PCS signals will be asserted for the transfer.

0 Negate the PCSn signal

1 Assert the PCSn signal

Note: This bitfield is only used in SPI master mode

16–31 TXDATA

[0:15]

Transmit data. Holds SPI data to be transferred according to the associated SPI

command.

Note: TXDATA is used in master and slave modes.

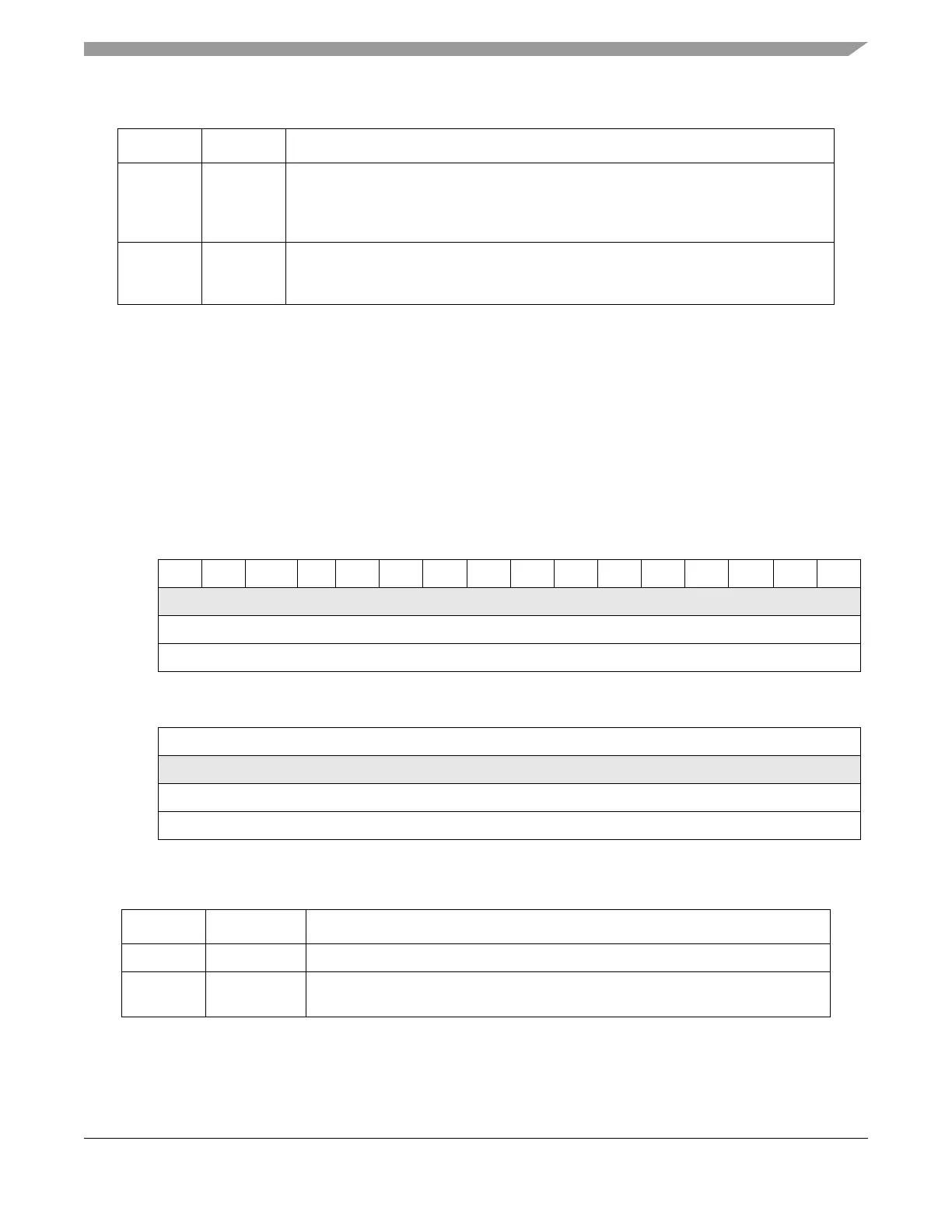

01 23456789101112131415

R00 00000000000000

W

Reset00 00000000000000

Reg Addr Base + 0x0038

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RRXDATA

W

Reset00 00000000000000

Reg Addr Base + 0x0038

Figure 20-9. DSPI POP RX FIFO Register (DSPIx_POPR)

Table 20-9. DSPIx_POPR Field Descriptions

Bits Name Description

0–15 — Reserved, should be cleared.

16–31 RXDATA

[0:15]

Received data. The RXDATA field contains the SPI data from the RX FIFO entry

pointed to by the pop next data pointer (POPNXTPTR).

Table 20-8. DSPIx_PUSHR Field Descriptions

Bits Name Description

Loading...

Loading...