MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

22-10 Freescale Semiconductor

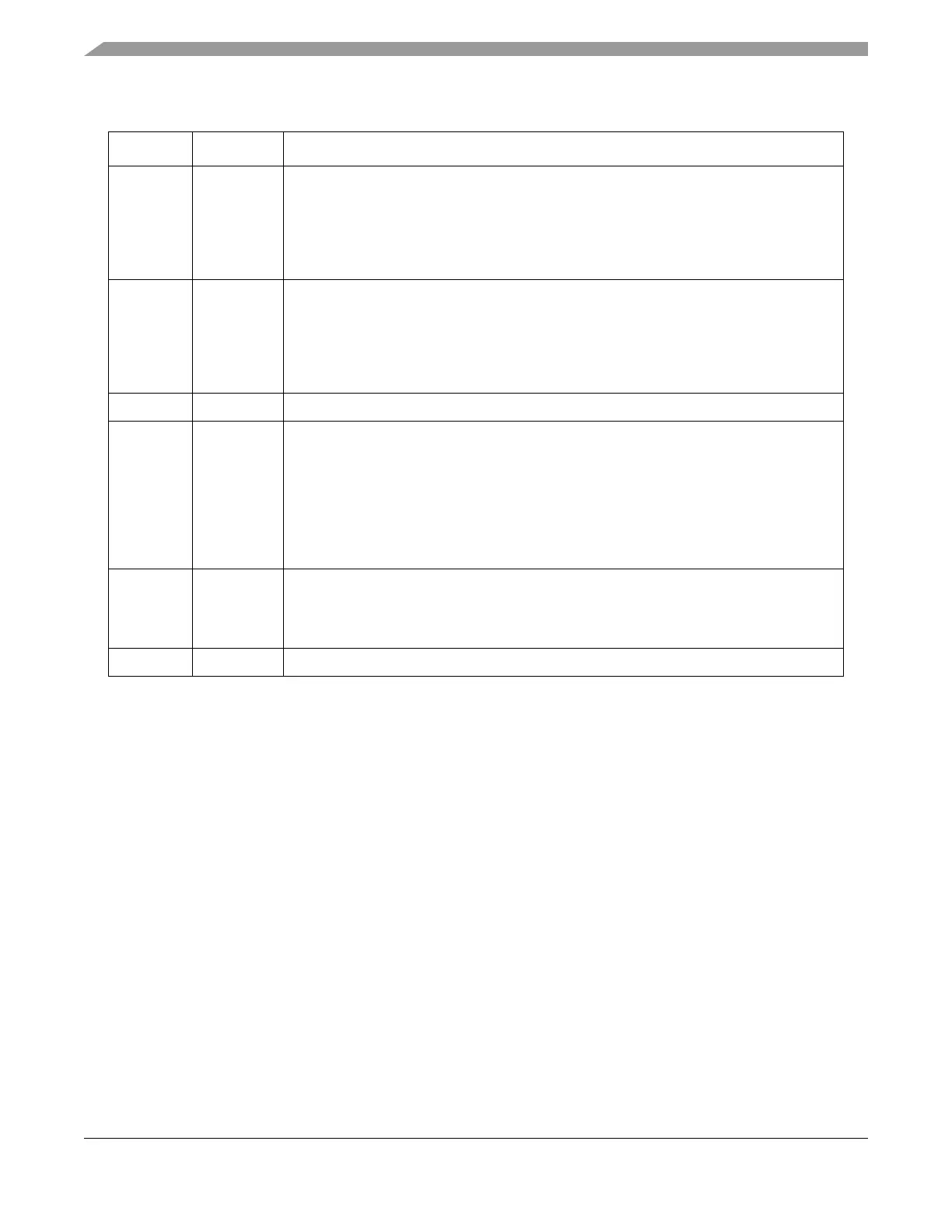

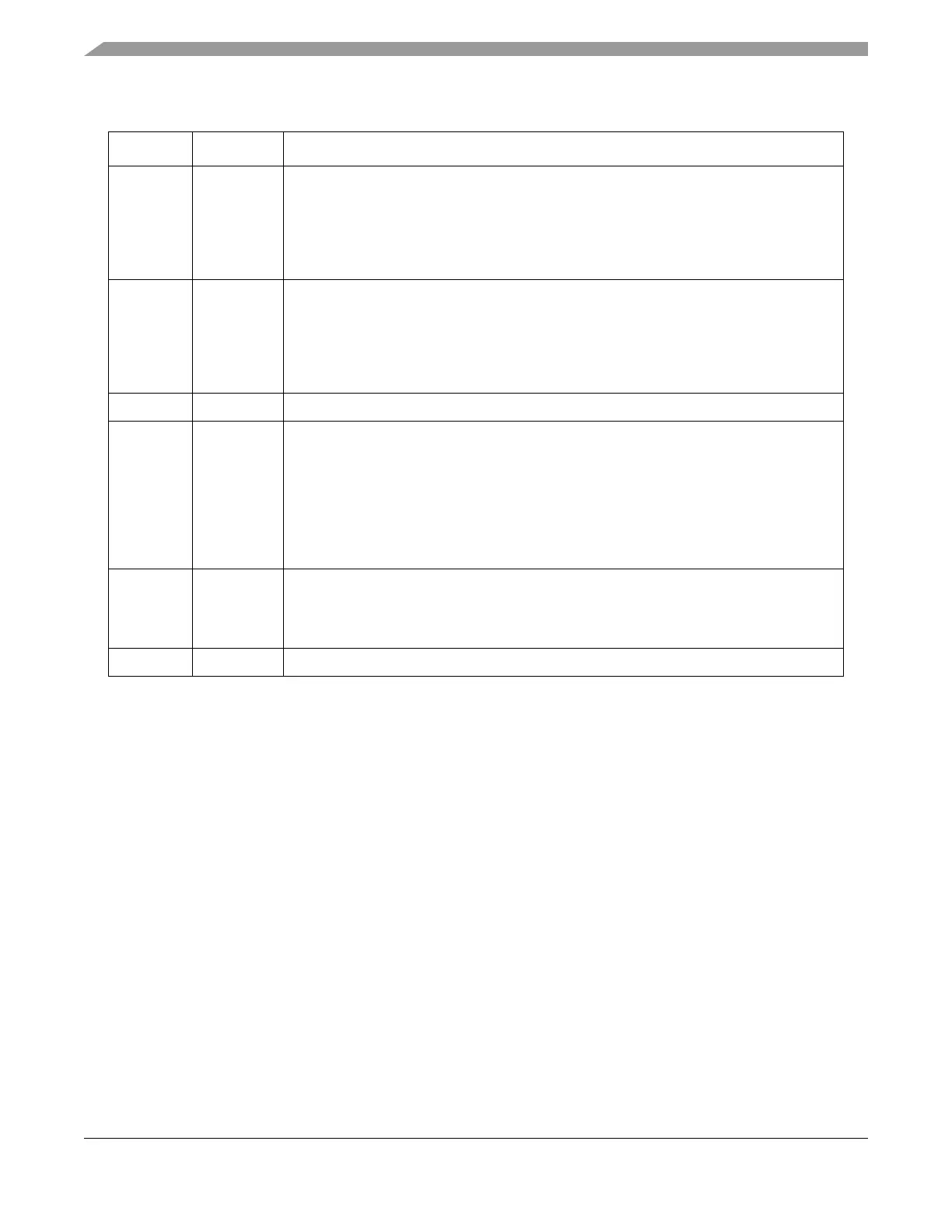

Table 22-7. CANx_MCR Field Descriptions

Bits Name Description

0 MDIS Module disable. Controls whether FlexCAN2 is enabled or not. When disabled, FlexCAN2

shuts down the clock to the CAN protocol interface and message buffer management

submodules. This is the only bit in CANx_MCR not affected by soft reset. See

Section 22.4.6.2, “Module Disabled Mode,” for more information.

0 Enable the FlexCAN2 module

1 Disable the FlexCAN2 module

1 FRZ Freeze enable. Specifies the FlexCAN2 behavior when the HALT bit in the CANx_MCR is

set or when debug mode is requested at MCU level. When FRZ is asserted, FlexCAN2 is

enabled to enter freeze mode. Negation of this bit field causes FlexCAN2 to exit from

freeze mode.

0 Not enabled to enter freeze mode

1 Enabled to enter freeze mode

2 — Reserved.

3 HALT Halt FlexCAN. Assertion of this bit puts the FlexCAN2 module into freeze mode if FRZ is

asserted. The CPU should clear it after initializing the message buffers and CANx_CR. If

FRZ is set, no reception or transmission is performed by FlexCAN2 before this bit is

cleared. While in freeze mode, the CPU has write access to the CANx_ECR, that is

otherwise read-only. Freeze mode cannot be entered while FlexCAN2 is disabled. See

Section 22.4.6.1, “Freeze Mode,” for more information.

0 No freeze mode request.

1 Enters freeze mode if the FRZ bit is asserted.

4 NOTRDY FlexCAN2 not ready. Indicates that FlexCAN2 is either disabled or in freeze mode. It is

negated once FlexCAN2 has exited these modes.

0 FlexCAN2 module is either in normal mode, listen-only mode or loop-back mode

1 FlexCAN2 module is either disabled or freeze mode

5 — Reserved.

Loading...

Loading...