Power Line Carrier

GARD 8000 SYS RFL Electronics

April 23, 2015 10-8 973.334.3100

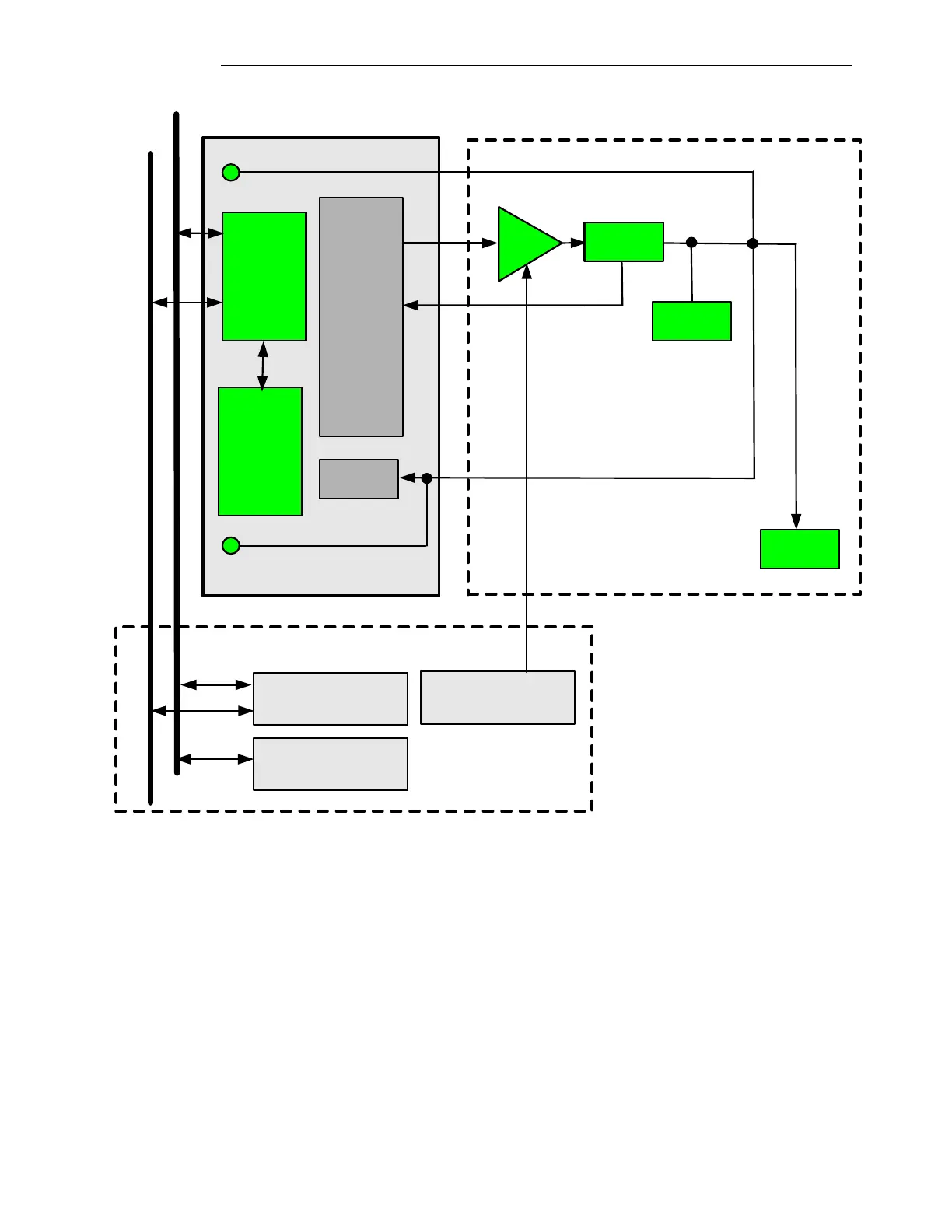

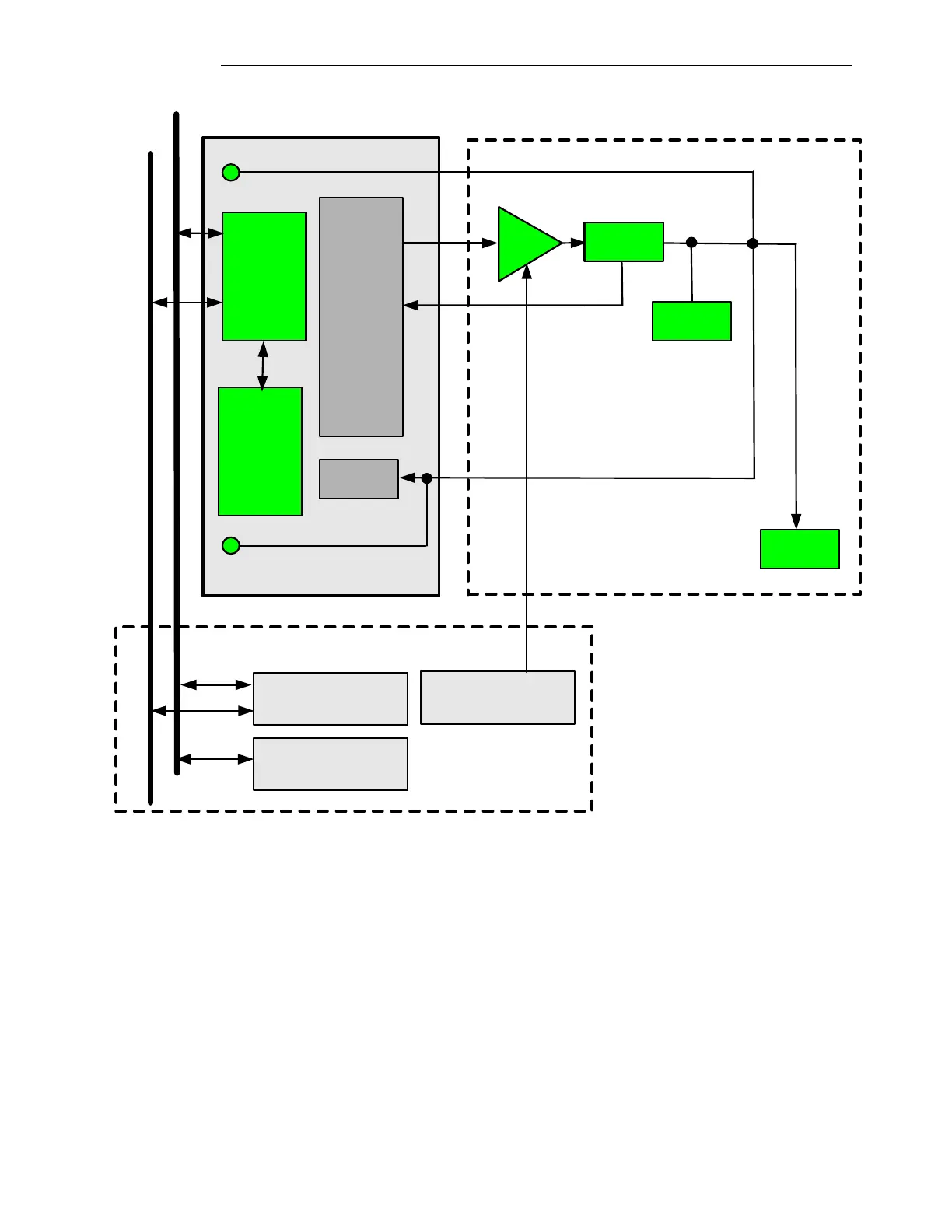

Midplane

Interface

Circuit

FPGA Circuit

Transceiver

Circuit

Control

Bus

Logic Bus

10W

Power

Amp

RX Atten.

TX Filter

Digital Module

Analog Module

Existing GARD Hardware

Controller/Logic +/-18V Power Supply

Discrete I/O

RPM

Line I/F

Components

TX Power Monitor

Figure 10-3. GARD 8000 PLC On/Off Block Diagram

On/Off Systems transmit and receive on the same frequency. Therefore, the local receiver cannot

differentiate between remote transmissions and local transmissions. In addition, checkback sequences

are detected as a sequence of trip events. The local receiver will report all trip events through the Logic

Bus interface whether the source is from local transmissions, checkback sequences, or real trips. It is

up to the logging mechanism in the Logic Controller to filter out unwanted SOE reports. To aid in this

filtering the module will indicate that a test is in process through a bit on the logic bus that is active

while a test is ongoing in a master or while an incoming code is detected in a remote.

The performance of On/Off operation is defined by the Maximum Trip Transport Delay, Dependability

and Security.

Loading...

Loading...