MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 22-23

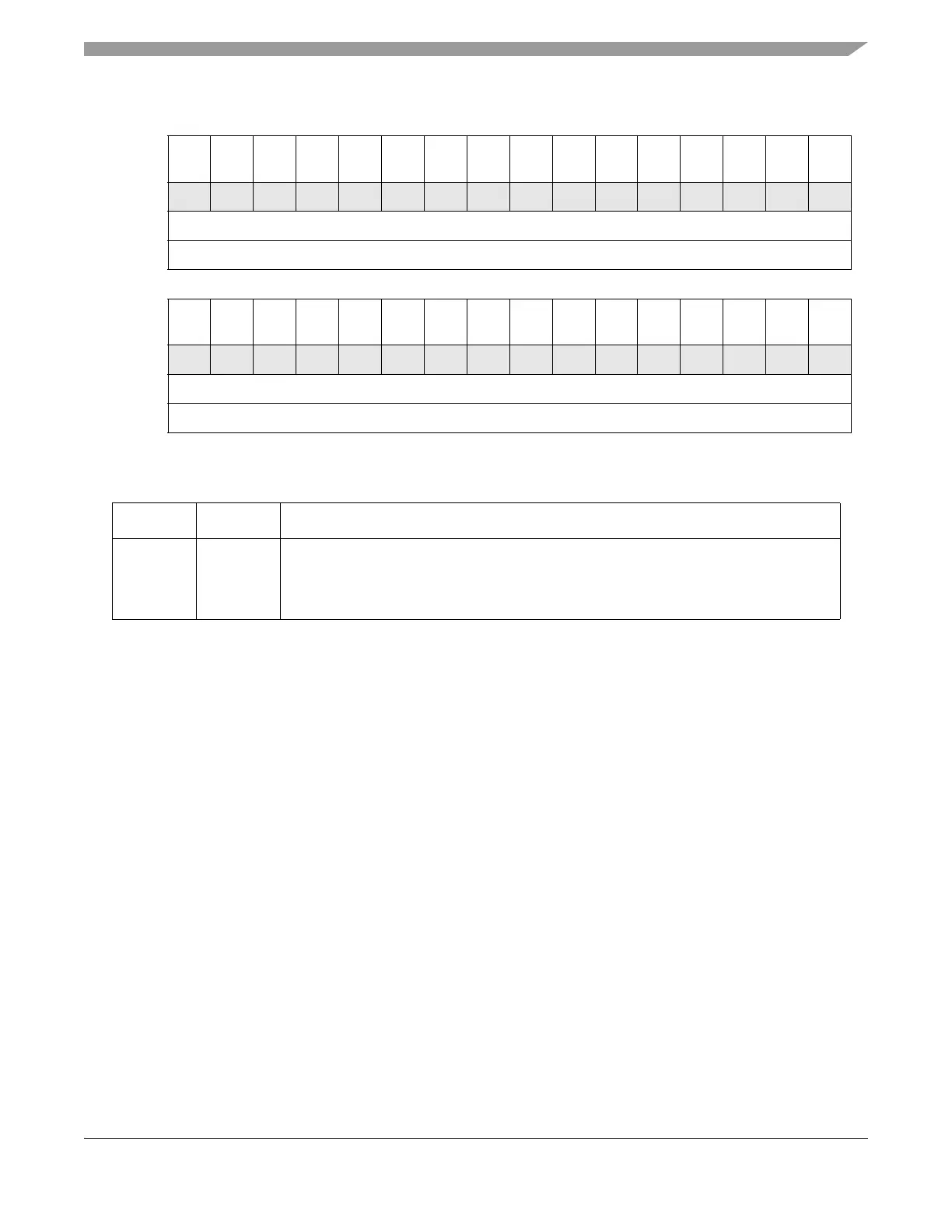

0123456789101112131415

RBUF

31I

BUF

30I

BUF

29I

BUF

28I

BUF

27I

BUF

26I

BUF

25

BUF

24I

BUF

23I

BUF

22I

BUF

21I

BUF

20I

BUF

19I

BUF

18I

BUF

17I

BUF

16I

W

w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset0000000000000000

Reg Addr Base + 0x0030

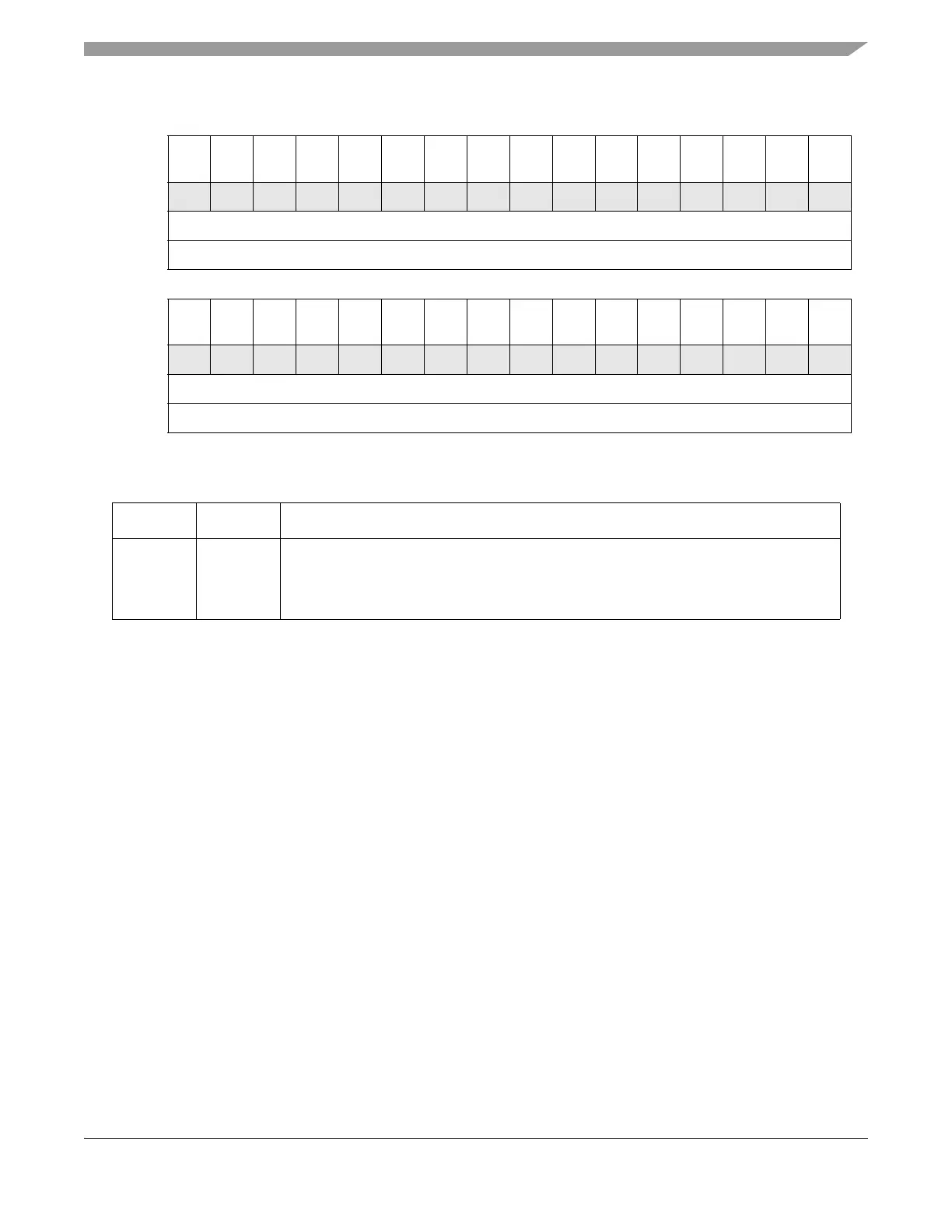

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RBUF

15I

BUF

14I

BUF

13I

BUF

12I

BUF

11I

BUF

10I

BUF

09I

BUF

08I

BUF

07I

BUF

06I

BUF

05I

BUF

04I

BUF

03I

BUF

02I

BUF

01I

BUF

00I

W

w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset0000000000000000

Reg Addr Base + 0x0030

Figure 22-12. Interrupt Flags Low Register (CANx_IFRL)

Table 22-15. CANx_IFRL Field Descriptions

Bits Name Description

0–31 BUFnI Message buffer n interrupt. Each bit represents the respective FlexCAN2 message buffer

(MB31 to MB0) interrupt. Write 1 to clear.

0 No such occurrence

1 The corresponding buffer has successfully completed transmission or reception.

Loading...

Loading...