MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

22-22 Freescale Semiconductor

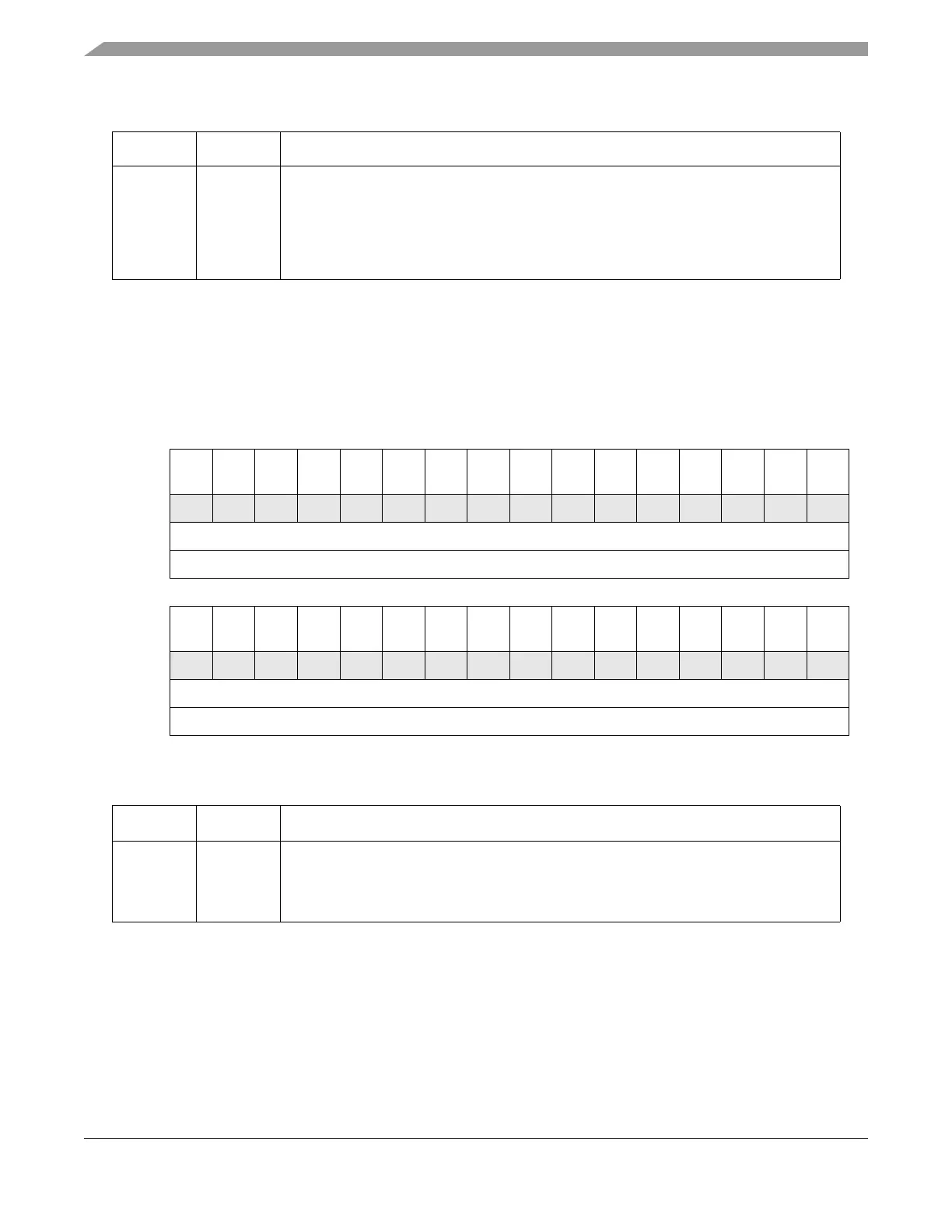

22.3.3.9 Interrupt Flags High Register (CANx_IFRH)

CANx_IFRH defines the flags for 32 message buffer interrupts. It contains one interrupt flag bit per buffer.

Each successful transmission or reception sets the corresponding IFRH bit. If the corresponding IMRH bit

is set, an interrupt will be generated. The interrupt flag may be cleared by writing it to 1. Writing 0 has no

effect.

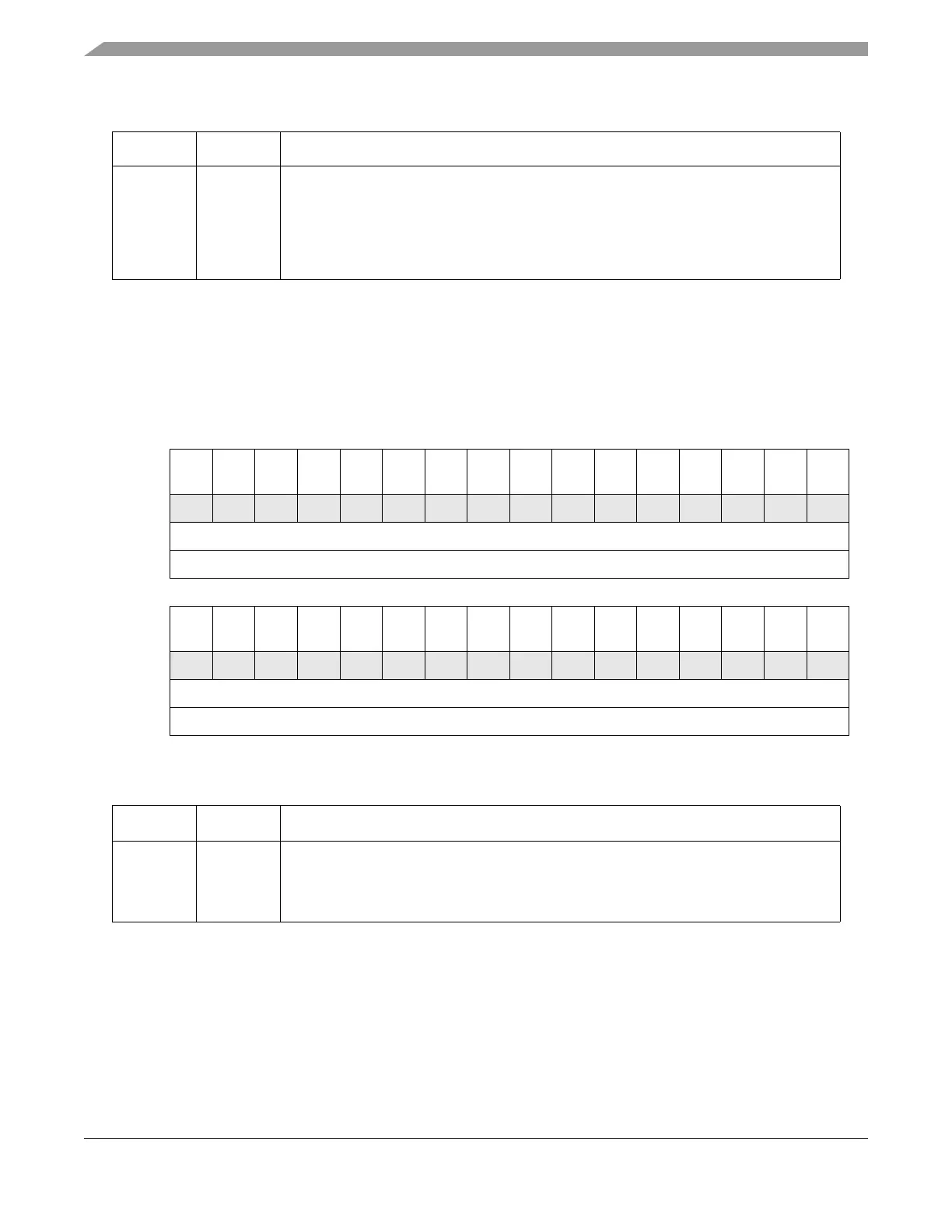

22.3.3.10 Interrupt Flags Low Register (CANx_IFRL)

CANx_IFRL defines the flags for 32 message buffer interrupts. It contains one interrupt flag bit per buffer.

Each successful transmission or reception sets the corresponding IFRL bit. If the corresponding IMRL bit

is set, an interrupt will be generated. The interrupt flag may be cleared by writing it to 1. Writing 0 has no

effect.

Table 22-13. CANx_IMRL Field Descriptions

Bits Name Description

0–31 BUFnM Message buffer n mask. Enables or disables the respective FlexCAN2 message buffer

(MB31 to MB0) Interrupt.

0 The corresponding buffer Interrupt is disabled

1 The corresponding buffer Interrupt is enabled

Note: Setting or clearing a bit in the IMRL register can assert or negate an interrupt

request, respectively.

0123456789101112131415

RBUF

63I

BUF

62I

BUF

61I

BUF

60I

BUF

59I

BUF

58I

BUF

57I

BUF

56I

BUF

55I

BUF

54I

BUF

53I

BUF

52I

BUF

51I

BUF

50I

BUF

49I

BUF

48I

W w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset0000000000000000

Reg Addr Base + 0x002C

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RBUF

47I

BUF

46I

BUF

45I

BUF

44I

BUF

43I

BUF

42I

BUF

41I

BUF

40I

BUF

39I

BUF

38I

BUF

37I

BUF

36I

BUF

35I

BUF

34I

BUF

33I

BUF

32I

W

w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset0000000000000000

Reg Addr Base + 0x002C

Figure 22-11. Interrupt Flags High Register (CANx_IFRH)

Table 22-14. CANx_IFRH Field Descriptions

Bits Name Description

0–31 BUFnI Message buffer n interrupt. Each bit represents the respective FlexCAN2 message buffer

(MB63–MB32) interrupt. Write 1 to clear.

0 No such occurrence

1 The corresponding buffer has successfully completed transmission or reception.

Loading...

Loading...