MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

25-74 Freescale Semiconductor

Table 25-46. DC1 Field Description

Bit Name Description

31 OPC

1

1

The output port mode control bit (OPC) and MCKO divide bits (MCK_DIV) are shown for clarity. These

functions are controlled globally by the NPC port control register (PCR).

Output port mode control

0 Reduced port mode configuration

1 Full port mode configuration

30–29 MCK_DIV

1

MCK_DIV - nexus message clock divide ratio

00 MCKO is 1x system bus clock freq.

01 MCKO is 1/2x system bus clock freq.

10 MCKO is 1/4x system bus clock freq.

11 MCKO is 1/8x system bus clock freq.

28–27 EOC EVTO

control

00 EVTO upon occurrence of watchpoint (internal or external)

01 EVTO

upon entry into system-level debug mode (ipg_debug)

1X Reserved

26–25 – Reserved, read as 0.

24 WEN Watchpoint trace enable

0 Watchpoint messaging disabled

1 Watchpoint messaging enabled.

23–5 – Reserved, read as 0.

4–3 EIC EVTI

control

00 EVTI for synchronization (Data Trace)

01 Reserved

10 EVTI

disabled for this module

11 Reserved

2–0 TM Trace mode

000 No Trace

1XX Reserved

X1X Data trace enabled

XX1 Reserved

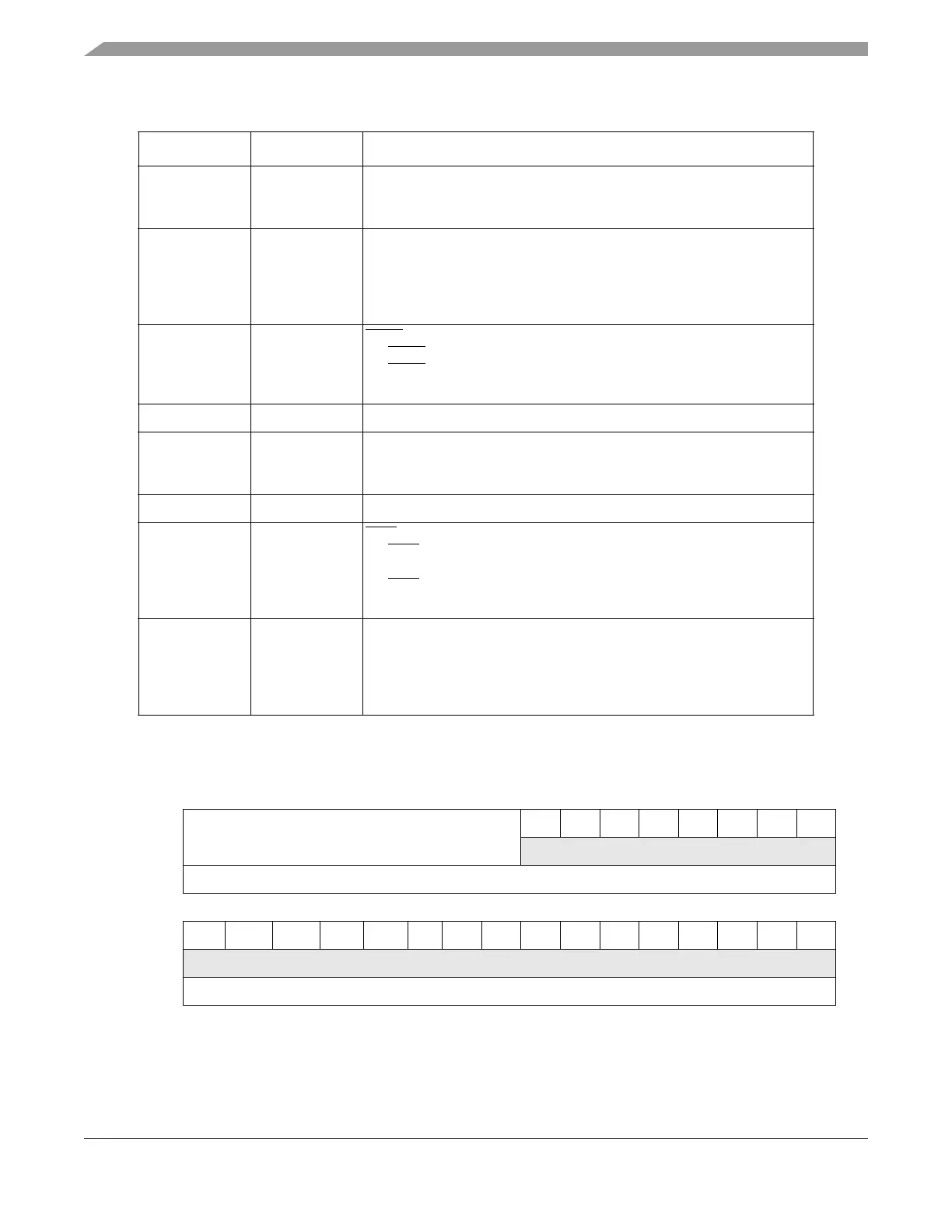

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R EWC 00000000

W

Reset0 0 0 0 000000000000

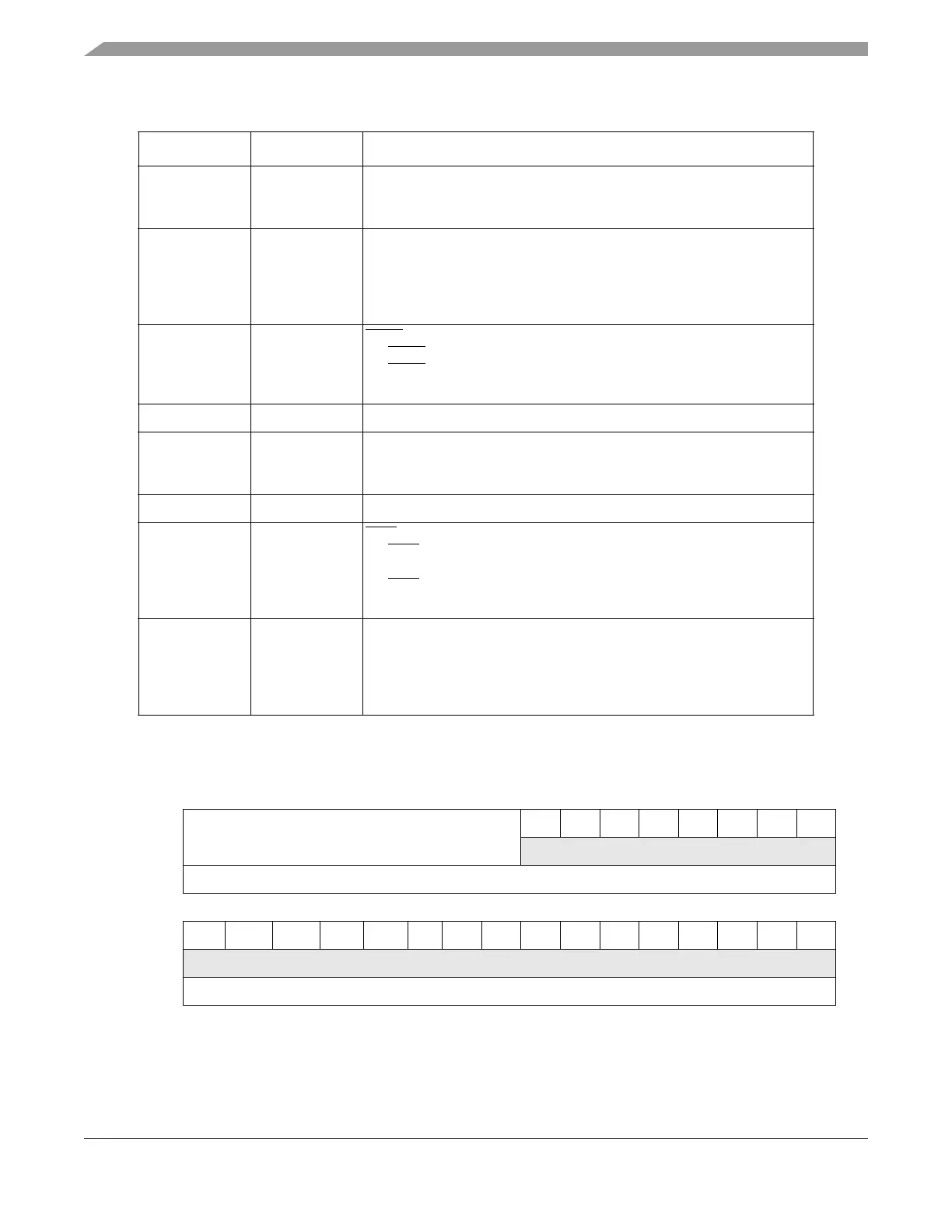

1514131211109876543210

R0 0 0 0 000000000000

W

Reset0 0 0 0 000000000000

Figure 25-54. Development Control Register 2 (DC2)

Loading...

Loading...