MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor A-25

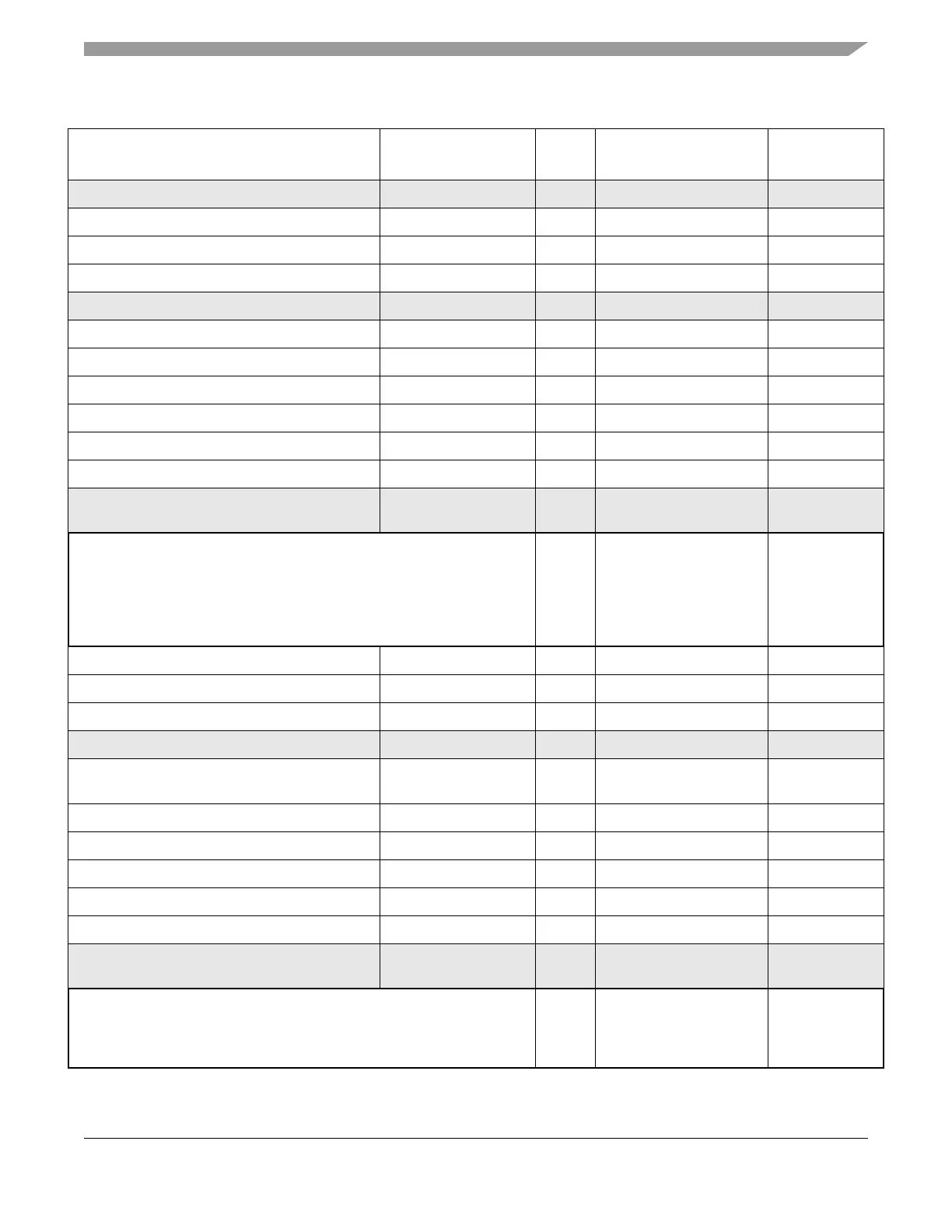

Reserved — — Base + (0x08D6-0x08FF)

eQADC trigger input select register SIU_ETISR 32-bits Base + 0x0900

External IRQ input select register SIU_EIISR 32-bits Base + 0x0904

DSPI input select register SIU_DISR 32-bits Base + 0x0908

Reserved — — Base + (0x090C-0x097F)

Chip configuration register SIU_CCR 32-bits Base + 0x0980

External clock control register SIU_ECCR 32-bits Base + 0x0984

Compare A high register SIU_CARH 32-bits Base + 0x0988

Compare A low register SIU_CARL 32-bits Base + 0x098C

Compare B high register SIU_CBRH 32-bits Base + 0x0990

Compare B low register SIU_CBRL 32-bits Base + 0x0994

Reserved — — (Base + 0x0998)-

0xC3F9_FFFF)

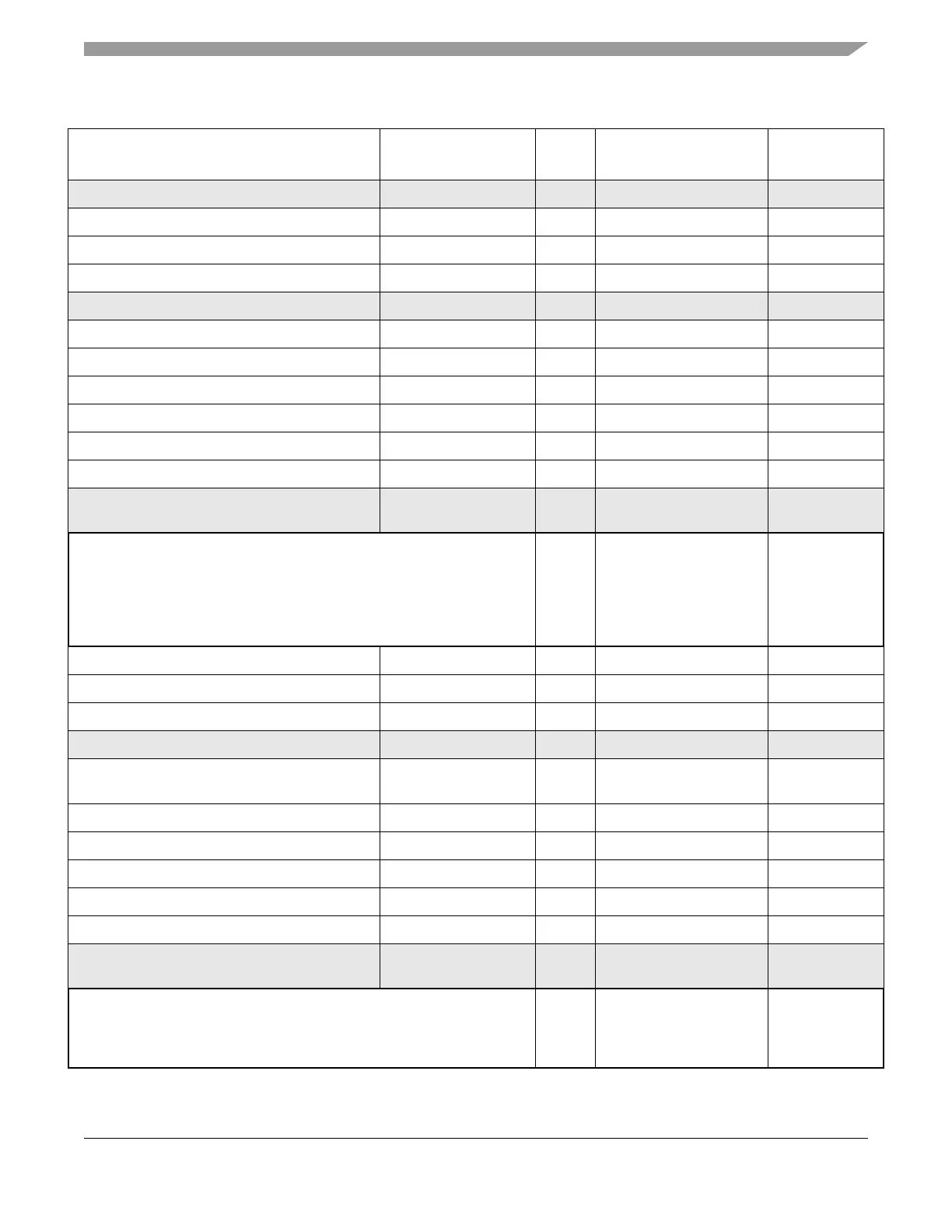

Enhanced Modular Input/Output Subsystem (eMIOS)

0xC3FA_0000 Chapter 17,

“Enhanced

Modular

Input/Output

Subsystem

(eMIOS)”

Module configuration register EMIOS_MCR 32-bit Base + 0x0000

Global flag register EMIOS_GFR 32-bit Base+ 0x0004

Output update disable register EMIOS_OUDR 32-bit Base + 0x0008

Reserved — — Base + (0x000C-0x001F)

Unified channel n, where n = 0-23 UC base addresses

(UCn)

Base + (0x0020 * (n+1))

Channel A data register n EMIOS_CADRn 32-bit UCnBase + 0x00

Channel B data register n EMIOS_CBDRn 32-bit UCnBase + 0x04

Channel counter register n EMIOS_CCNTRn 32-bit UCnBase + 0x08

Channel control register n EMIOS_CCRn 32-bit UCnBase + 0x0C

Channel status register n EMIOS_CSRn 32-bit UCnBase + 0x10

Reserved — — (UCnBase + 0x14)-

0xC3FB_FFFF

Enhanced Time Processing Unit (eTPU)

0xC3FC_0000 Chapter 18,

“Enhanced Time

Processing Unit

(eTPU)”

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...