MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor A-27

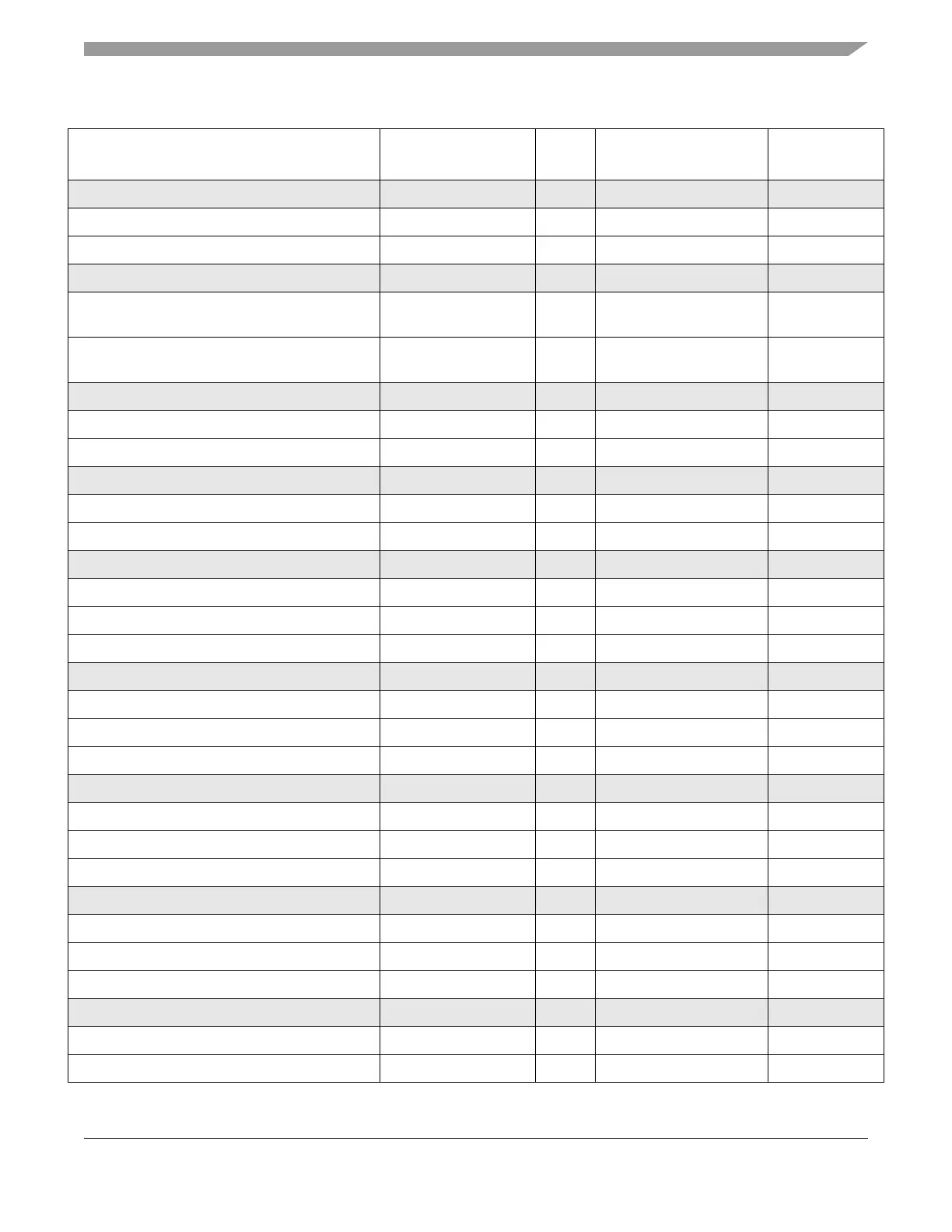

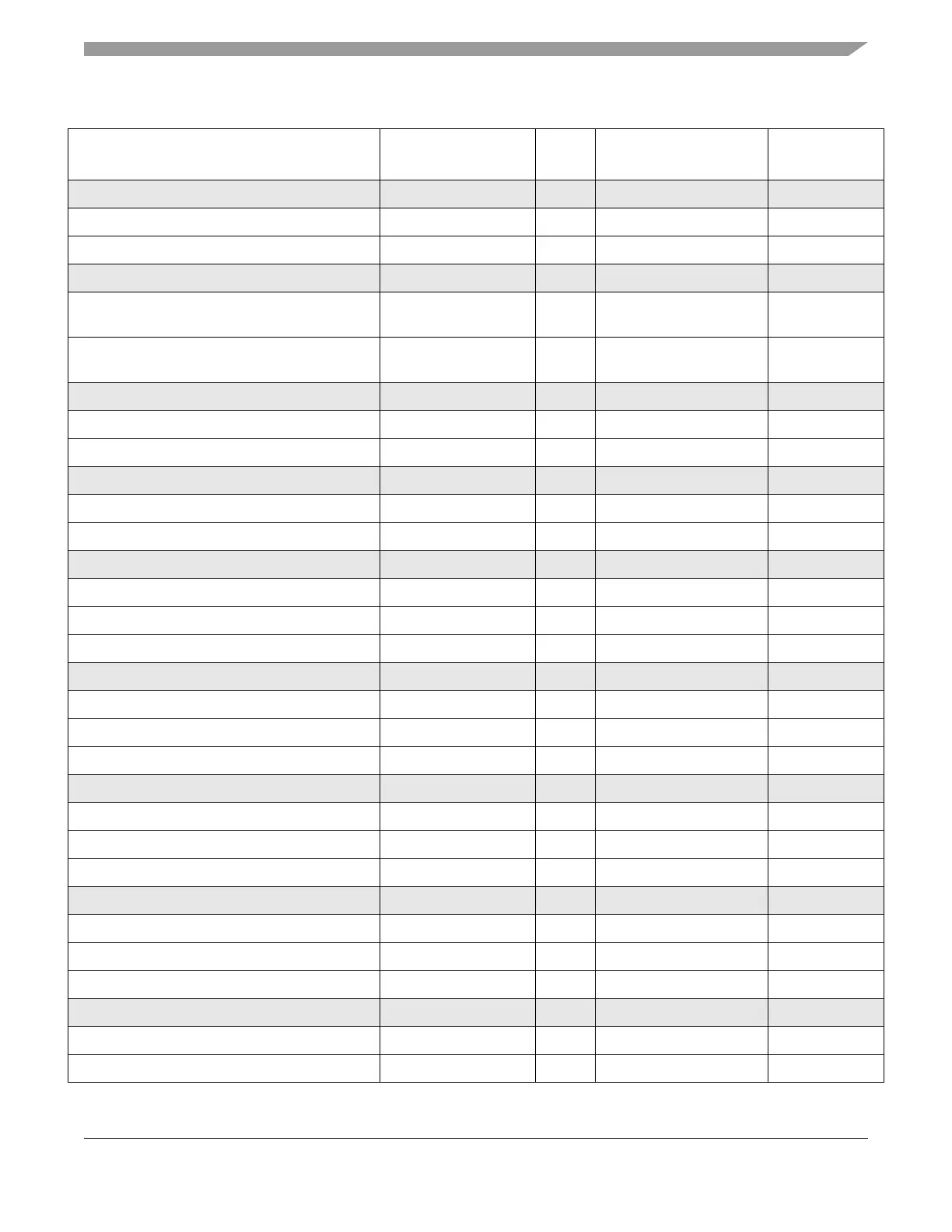

Reserved — — Base + (0x0238-0x023F)

eTPU A channel interrupt enable register ETPU_CIER_A 32-bit Base + 0x0240

eTPU B channel interrupt enable register

2

ETPU_CIER_B

2

32-bit Base + 0x0244

Reserved — — Base + (0x0248-0x024F)

eTPU A channel data transfer request enable

register

ETPU_CDTRER_A 32-bit Base + 0x0250

eTPU B channel data transfer request enable

register

2

ETPU_CDTRER_B

2

32-bit Base + 0x0254

Reserved — — Base + (0x0258-0x027F)

eTPU A channel pending service status register ETPU_CPSSR_A 32-bit Base + 0x0280

eTPU B channel pending service status register

2

ETPU_CPSSR_B

2

32-bit Base + 0x0284

Reserved — — Base + (0x0288-0x028F)

eTPU A channel service status register ETPU_CSSR_A 32-bit Base + 0x0290

eTPU B channel service status register

2

ETPU_CSSR_B

2

32-bit Base + 0x0294

Reserved — — Base + (0x0298-0x03FF)

eTPU A channel 0 configuration register ETPU_C0CR_A 32-bit Base + 0x0400

eTPU A channel 0 status and control register ETPU_C0SCR_A 32-bit Base + 0x0404

eTPU A channel 0 host service request register ETPU_C0HSRR_A 32-bit Base + 0x0408

Reserved — — Base + (0x040C-0x040F)

eTPU A channel 1 configuration register ETPU_C1CR_A 32-bit Base + 0x0410

eTPU A channel 1 status and control register ETPU_C1SCR_A 32-bit Base + 0x0414

eTPU A channel 1 host service request register ETPU_C1HSRR_A 32-bit Base + 0x0418

Reserved — — Base + (0x041C-0x041F)

eTPU A channel 2 configuration register ETPU_C2CR_A 32-bit Base + 0x0420

eTPU A channel 2 status and control register ETPU_C2SCR_A 32-bit Base + 0x0424

eTPU A channel 2 host service request register ETPU_C2HSRR_A 32-bit Base + 0x0428

Reserved — — Base + (0x042C-0x042F)

eTPU A channel 3 configuration register ETPU_C3CR_A 32-bit Base + 0x0430

eTPU A channel 3 status and control register ETPU_C3SCR_A 32-bit Base + 0x0434

eTPU A channel 3 host service request register ETPU_C3HSRR_A 32-bit Base + 0x0438

Reserved — — Base + (0x043C-0x043F)

eTPU A channel 4 configuration register ETPU_C4CR_A 32-bit Base + 0x0440

eTPU A channel 4 status and control register ETPU_C4SCR_A 32-bit Base + 0x0444

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...