MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor A-53

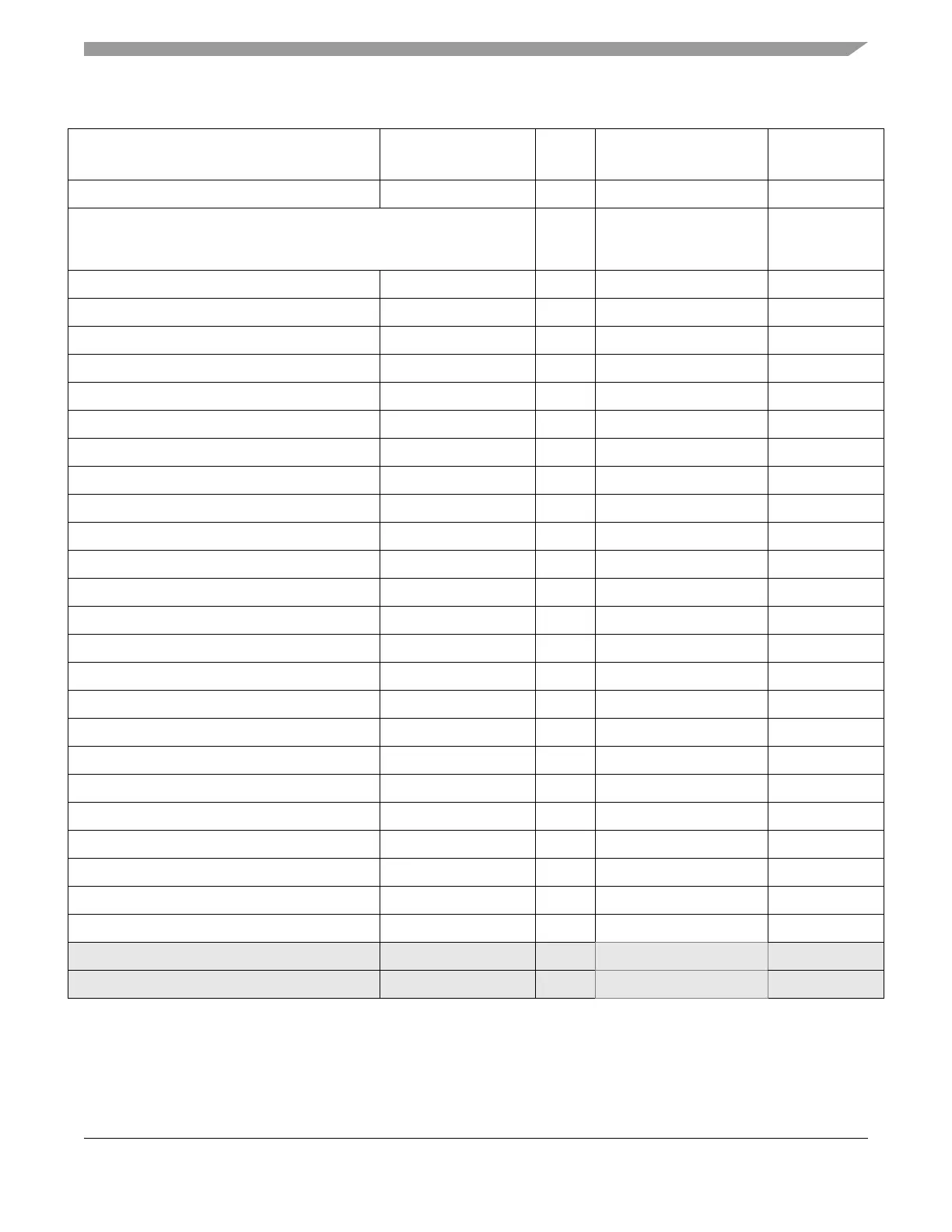

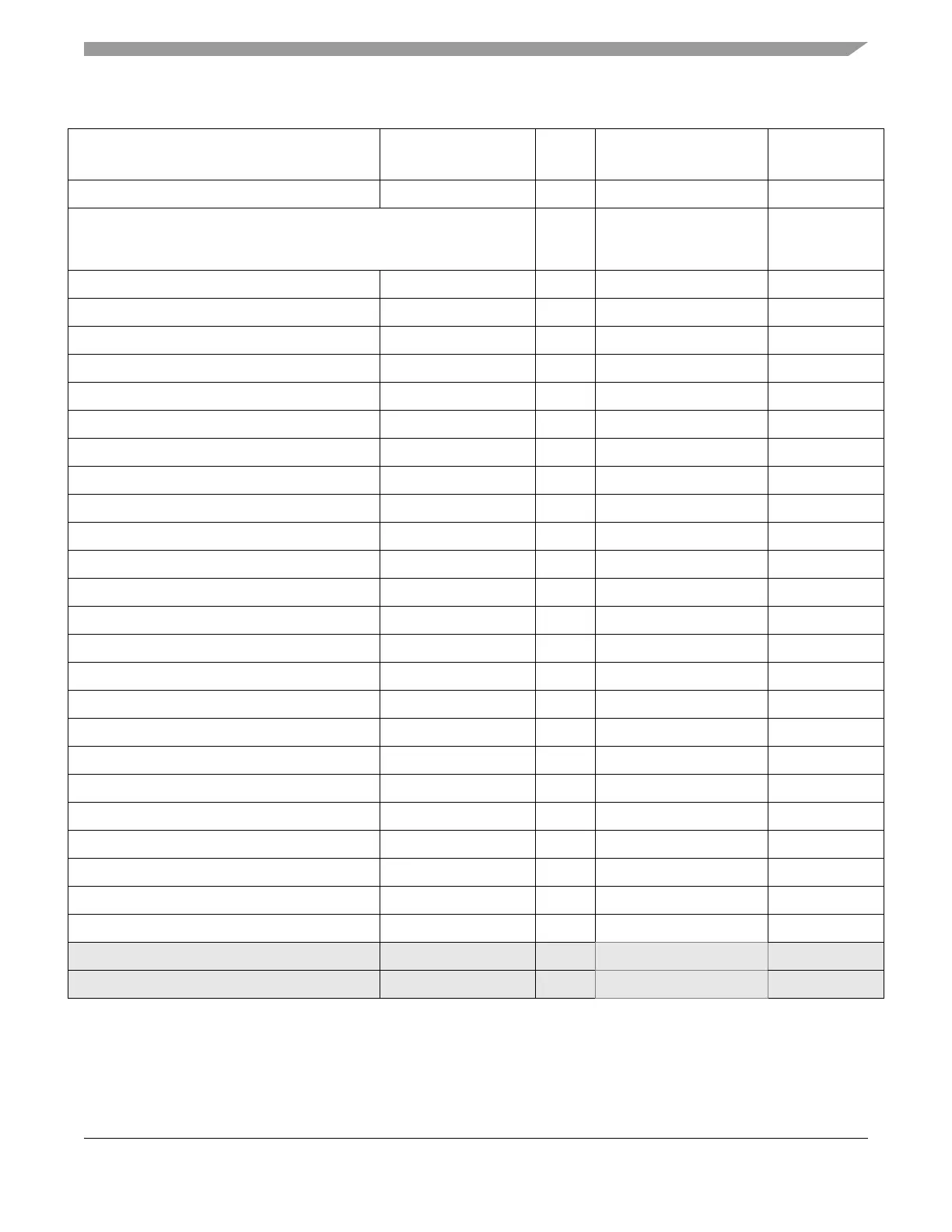

Priority select register 307 INTC_PSR307 8-bit Base + 0x0173

Fast Ethernet Controller (FEC)

0xFFF4_C000 Chapter 14 “Fast

Ethernet

Controller (FEC)”

Interrupt Event Register EIR 32-bit Base + 0x0004

Interrupt Mask Register EIMR 32-bit Base + 0x0008

Receive Descriptor Active Register RDAR 32-bit Base + 0x0010

Transmit Descriptor Active Register TDAR 32-bit Base + 0x0014

Ethernet Control Register ECR 32-bit Base + 0x0024

MII Management Frame Register MMFR 32-bit Base + 0x0040

MII Speed Control Register MSCR 32-bit Base + 0x0044

MIB Control/Status Register MIBC 32-bit Base + 0x0064

Receive Control Register RCR 32-bit Base + 0x0084

Transmit Control Register TCR 32-bit Base + 0x00C4

MAC Address Low Register PALR 32-bit Base + 0x00E4

MAC Address Upper Register + Type Field PAUR 32-bit Base + 0x00E8

Opcode + Pause Duration OPD 32-bit Base + 0x00EC

Upper 32 bits of Individual Hash Table IAUR 32-bit Base + 0x0118

Lower 32 Bits of Individual Hash Table IALR 32-bit Base + 0x011C

Upper 32 bits of Group Hash Table GAUR 32-bit Base + 0x0120

Lower 32 bits of Group Hash Table GALR 32-bit Base + 0x0124

Transmit FIFO Watermark TFWR 32-bit Base + 0x0144

FIFO Receive Bound Register FRBR 32-bit Base + 0x014C

FIFO Receive FIFO Start Registers FRSR 32-bit Base + 0x0150

Pointer to Receive Descriptor Ring ERDSR 32-bit Base + 0x0180

Pointer to Transmit Descriptor Ring ETDSR 32-bit Base + 0x0184

Maximum Receive Buffer Size EMRBR 32-bit Base + 0x0188

MIB Block Counters MIB FFF4_C200

Reserved — — Base + (0xFFF0__8000)

Reserved — — Base + (0xFFF1_0000)

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...