MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

A-54 Freescale Semiconductor

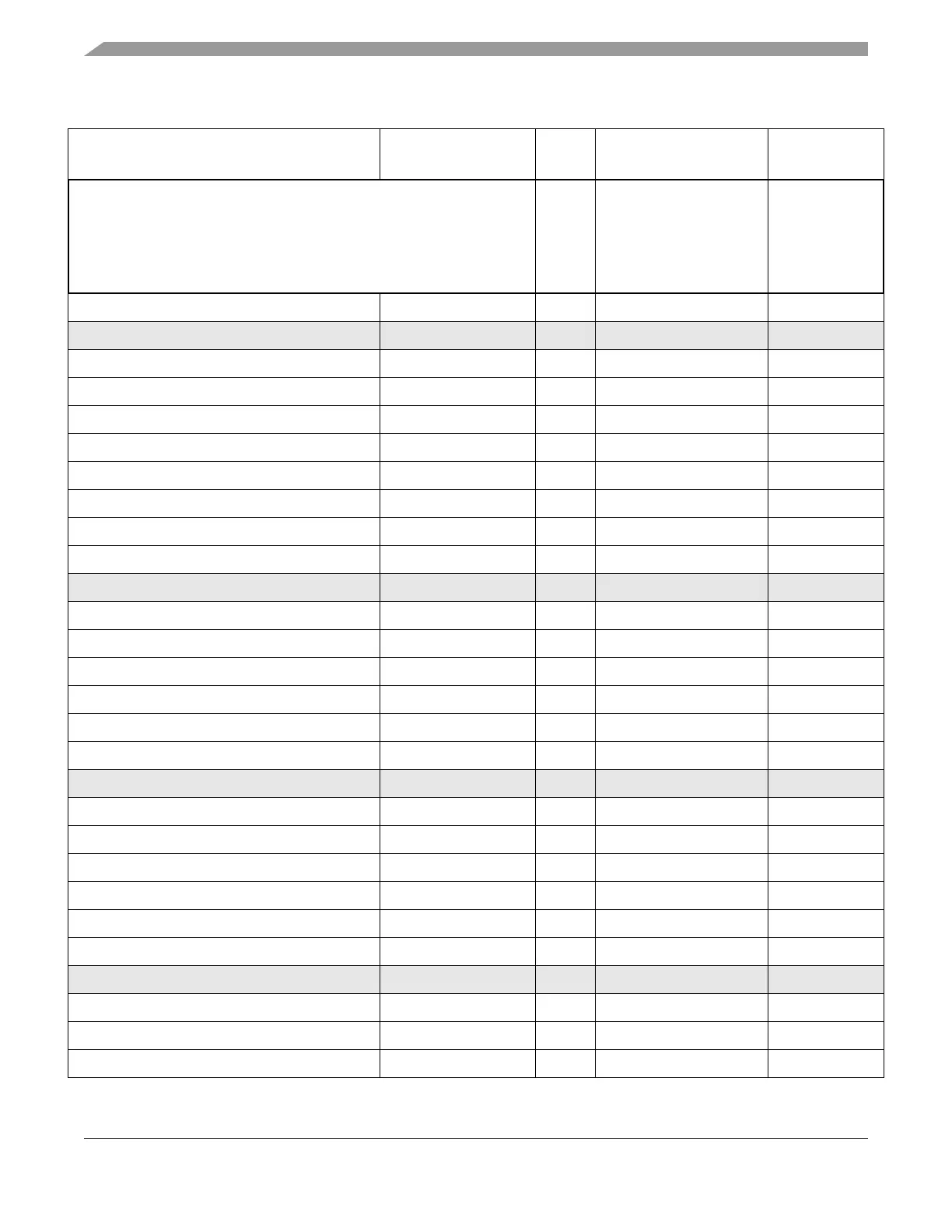

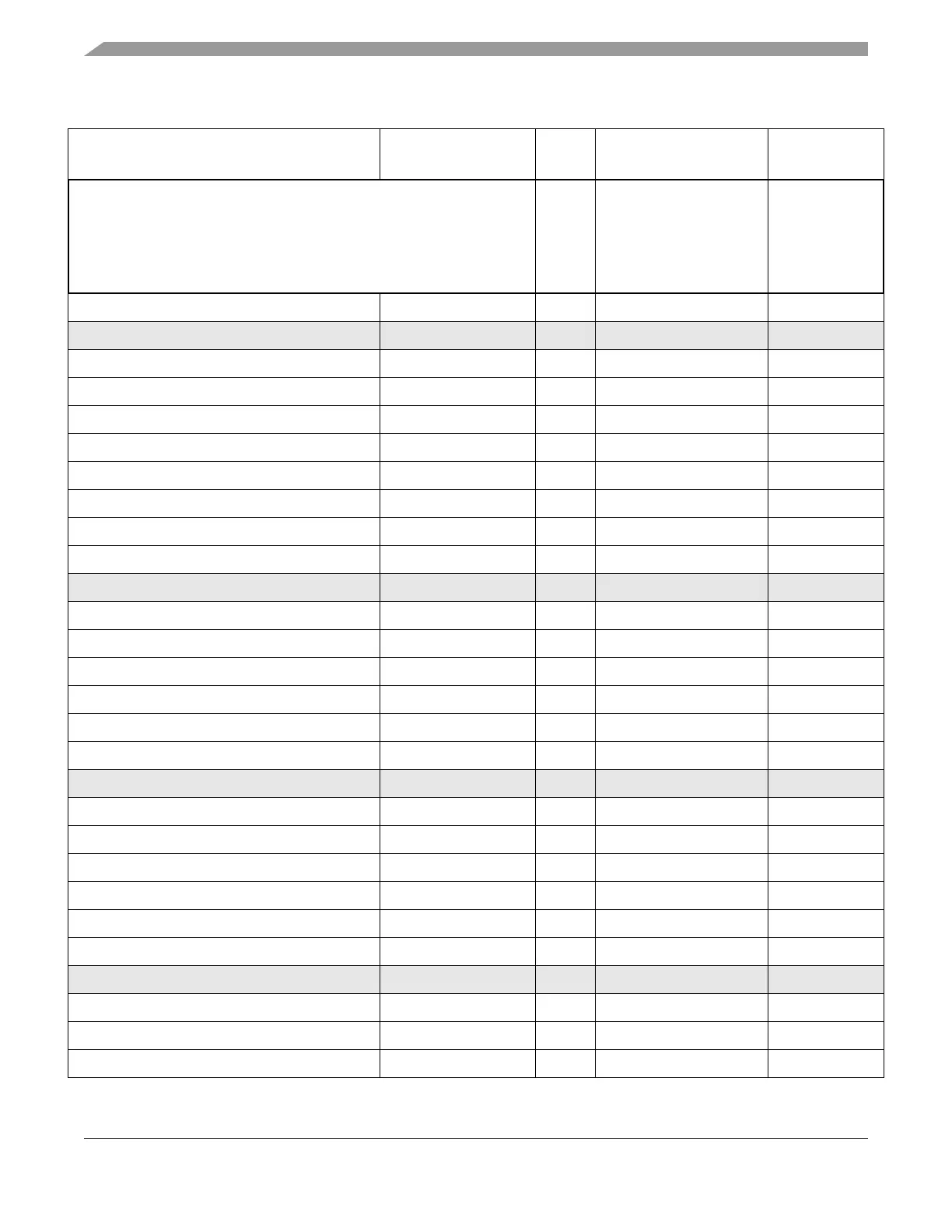

Enhanced Queued Analog-to-Digital Converter (eQADC)

0xFFF8_0000 Chapter 19,

“Enhanced

Queued

Analog-to-Digital

Converter

(eQADC)”

Module configuration register EQADC_MCR 32-bit Base + 0x0000

Reserved — — Base + (0x0004-0x0007)

Null message send format register EQADC_NMSFR 32-bit Base + 0x0008

External trigger digital filter register EQADC_ETDFR 32-bit Base + 0x000C

CFIFO push register 0 EQADC_CFPR0 32-bit Base +0x0010

CFIFO push register 1 EQADC_CFPR1 32-bit Base +0x0014

CFIFO push register 2 EQADC_CFPR2 32-bit Base +0x0018

CFIFO push register 3 EQADC_CFPR3 32-bit Base +0x001C

CFIFO push register 4 EQADC_CFPR4 32-bit Base +0x0020

CFIFO push register 5 EQADC_CFPR5 32-bit Base +0x0024

Reserved — — Base + (0x0028-0x002F)

Result FIFO pop register 0 EQADC_RFPR0 32-bit Base + 0x0030

Result FIFO pop register 1 EQADC_RFPR1 32-bit Base + 0x0034

Result FIFO pop register 2 EQADC_RFPR2 32-bit Base + 0x0038

Result FIFO pop register 3 EQADC_RFPR3 32-bit Base + 0x003C

Result FIFO pop register 4 EQADC_RFPR4 32-bit Base + 0x0040

Result FIFO pop register 5 EQADC_RFPR5 32-bit Base + 0x0044

Reserved — — Base + (0x0048-0x004F)

CFIFO control register 0 EQADC_CFCR0 16-bit Base + 0x0050

CFIFO control register 1 EQADC_CFCR1 16-bit Base + 0x0052

CFIFO control register 2 EQADC_CFCR2 16-bit Base + 0x0054

CFIFO control register 3 EQADC_CFCR3 16-bit Base + 0x0056

CFIFO control register 4 EQADC_CFCR4 16-bit Base + 0x0058

CFIFO control register 5 EQADC_CFCR5 16-bit Base + 0x005A

Reserved — — Base + (0x005C-0x005F)

Interrupt and DMA control register 0 EQADC_IDCR0 16-bit Base + 0x0060

Interrupt and DMA control register 1 EQADC_IDCR1 16-bit Base + 0x0062

Interrupt and DMA control register 2 EQADC_IDCR2 16-bit Base + 0x0064

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...