MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor A-59

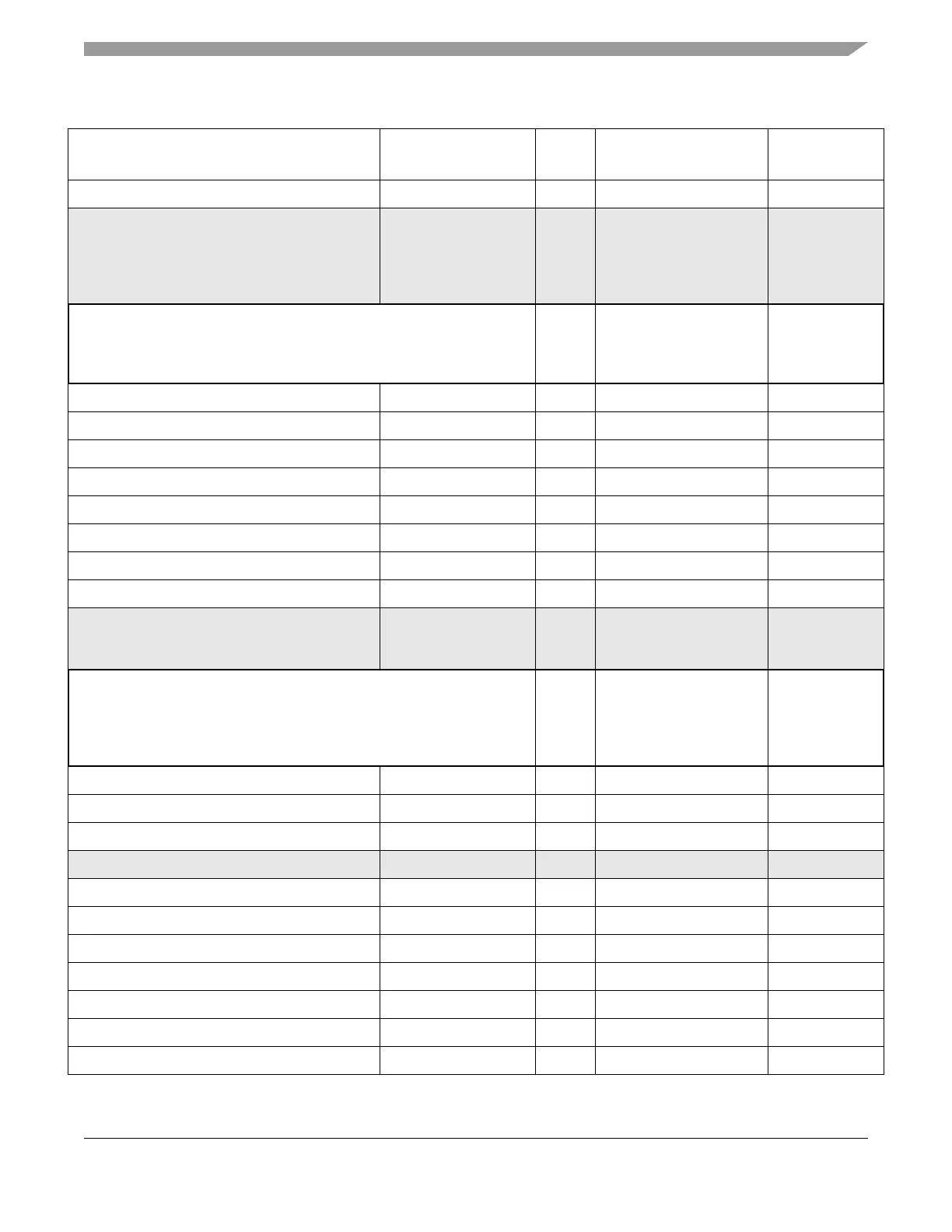

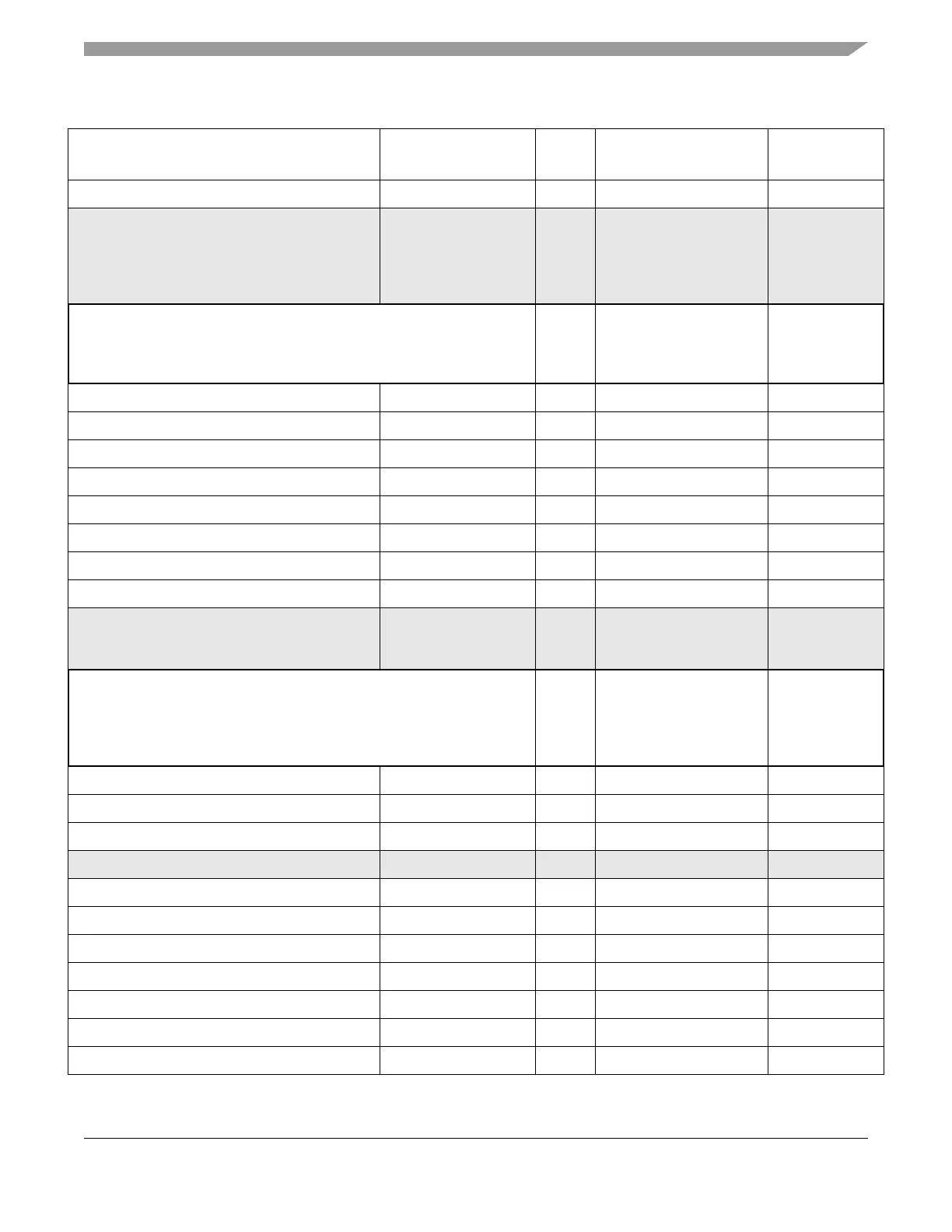

DSI deserialization data register DSPIx_DDR 32-bit Base + 0x00CC

Reserved — — (Base +0x00D0)-

(0xFFF9_3FFF) (A)

(0xFFF9_7FFF) (B)

(0xFFF9_BFFF) (C)

(0xFFFA_FFFF) (D)

Enhanced Serial Communication Interface (eSCIx)

0xFFFB_0000 (A)

0xFFFB_4000 (B)

Chapter 21,

“Enhanced Serial

Communication

Interface (eSCI)”

Control register 1 ESCIx_CR1 32-bit Base + 0x0000

Control register 2 ESCIx_CR2 16-bit Base + 0x0004

Data register ESCIx_DR 16-bit Base + 0x0006

Status register ESCIx_SR 32-bit Base + 0x0008

LIN control register ESCIx_LCR 32-bit Base + 0x000C

LIN transmit register ESCIx_LTR 32-bit Base + 0x0010

LIN receive register ESCIx_LRR 32-bit Base + 0x0014

LIN CRC polynomial register ESCIx_LPR 32-bit Base + 0x0018

Reserved — — (Base +0x001C)-

(0xFFFB_3FFF) (A)

(0xFFFB_7FFF) (B)

FlexCAN2 Controller Area Network (CANx)

0xFFFC_0000 (FlexCAN A)

0xFFFC_4000 (FlexCAN B)

2

0xFFFC_8000 (FlexCAN

C)

Chapter 22,

“FlexCAN2

Controller Area

Network”

Module configuration register CANx_MCR 32-bit Base + 0x0000

Control register CANx_CR 32-bit Base + 0x0004

Free running timer register CANx_TIMER 32-bit Base + 0x0008

Reserved — — Base + (0x000C-0x000F)

Receive global mask register CANx_RXGMASK 32-bit Base + 0x0010

Receive buffer 14 mask register CANx_RX14MASK 32-bit Base + 0x0014

Receive buffer 15 mask register CANx_RX15MASK 32-bit Base + 0x0018

Error counter register CANx_ECR 32-bit Base + 0x001C

Error and status register CANx_ESR 32-bit Base + 0x0020

Interrupt mask register high CANx_IMRH 32-bit Base + 0x0024

Interrupt mask register low CANx_IMRL 32-bit Base + 0x0028

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...