MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 5-9

1

In PBRIDGE_A_PACR0 and in PBRIDGE_B_PACR0, the BW0 bit is not writable.

2

The default value is 0b0000 for PACR peripheral access fields that are unused or not connected.

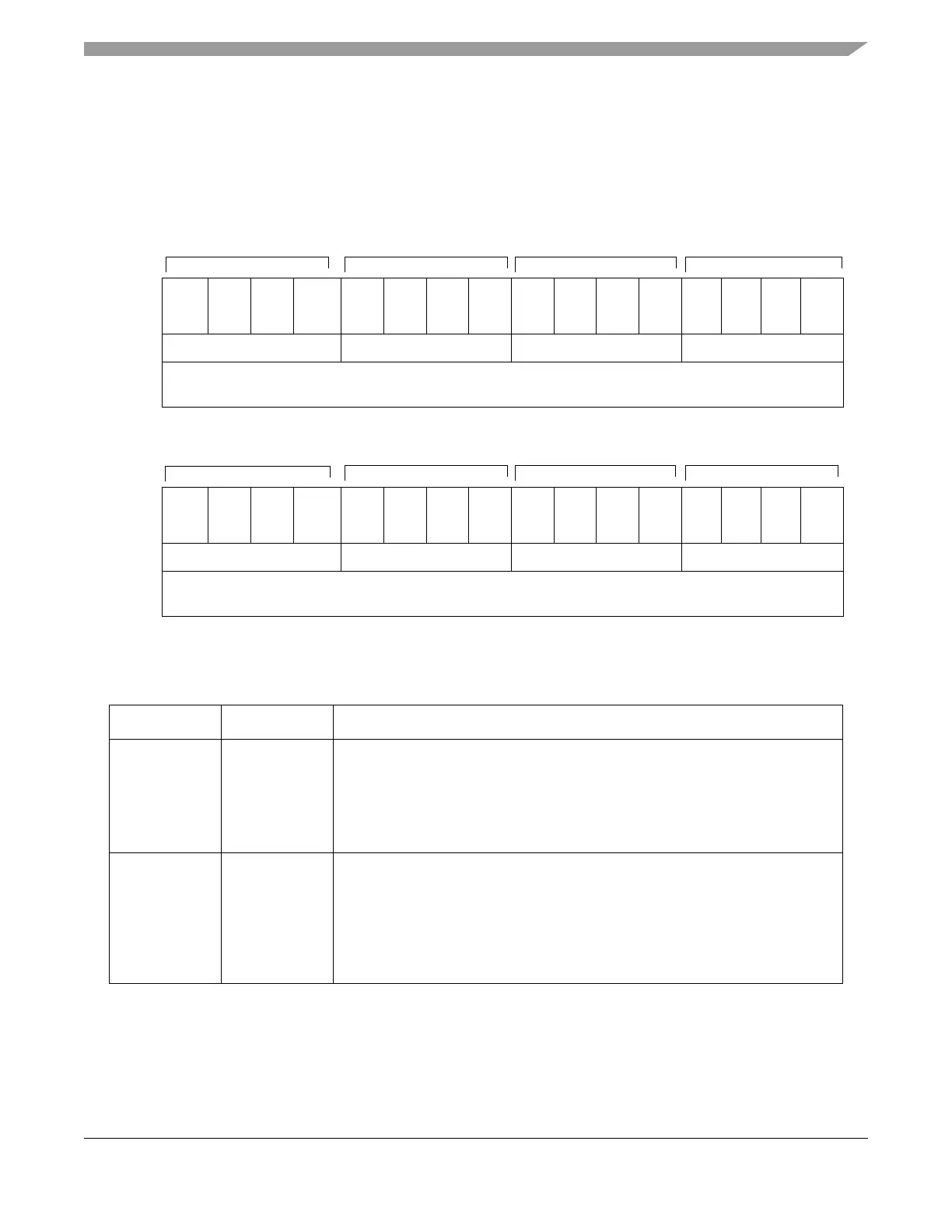

012 3 456789101112131415

R BW0 SP0 WP0 TP0 BW1 SP1 WP1 TP1 BW2 SP2 WP2 TP2 BW3 SP3 WP3 TP3

W

Reset0100 010001000100

Reg

Addr

Base + 0x0040 (PBRIDGE_x_OPACR0); Base + 0x000044 (PBRIDGE_x_OPACR1); Base + 0x0048

(PBRIDGE_x_OPACR2); Base + 0x004C (PBRIDGE_B_OPACR3)

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R BW4 SP4 WP4 TP4 BW5 SP5 WP5 TP5 BW6 SP6 WP6 TP6 BW7 SP7 WP7 TP7

W

Reset0100 010001000100

Reg

Addr

Base + 0x0040 (PBRIDGE_x_OPACR0); Base + 0x0044 (PBRIDGE_x_OPACR1); Base + 0x0048

(PBRIDGE_x_OPACR2); Base + 0x004C (PBRIDGE_B_OPACR3)

Figure 5-4. Off-platform Peripheral Access Control Registers (PBRIDGE_x_OPACRn)

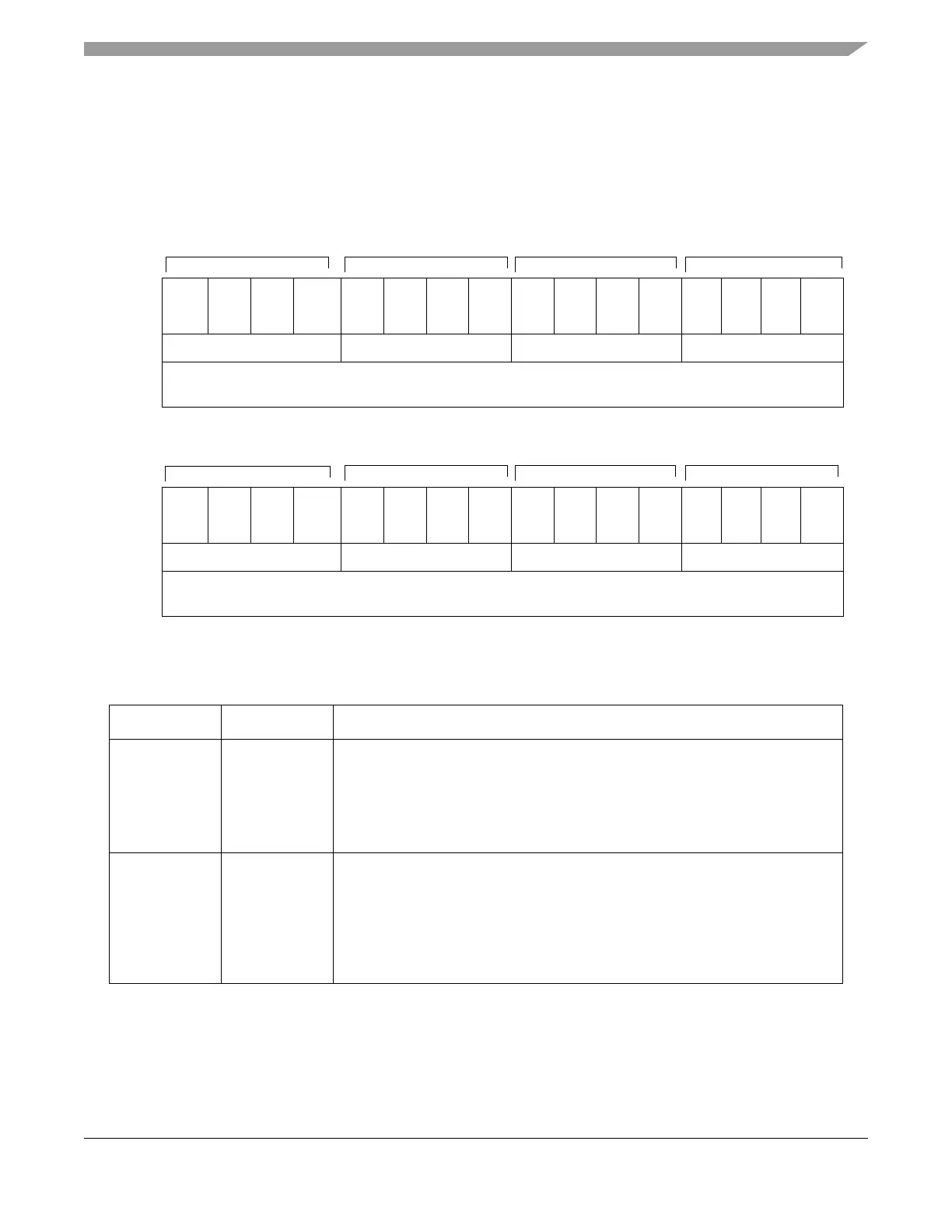

Table 5-5. PBRIDGE_x_PACRn and PBRIDGE_x_OPACRn

Field Descriptions

Bits Name Description

0, 4, 8, 12, 16,

20, 24, 28

BWn

1

Buffer writes. Determines whether write accesses to this peripheral are allowed to

be buffered. Write accesses not bufferable by default

0 Write accesses to this peripheral are not bufferable by the PBRIDGE.

1 Write accesses to this peripheral are allowed to be buffered by the PBRIDGE.

Note: In PBRIDGE_A_PACR0 and PBRIDGE_B_PACR0, the BW0 bit is not

writable.

1, 5, 9, 13, 17,

21, 25, 29

SPn Supervisor protect. Determines whether the peripheral requires supervisor

privilege level for access. Supervisor privilege level required by default.

0 This peripheral does not require supervisor privilege level for accesses.

1 This peripheral requires supervisor privilege level for accesses. The

PBRIDGE_x_MPCR[MPLy] control bit for the master must be set. If not, the

access is terminated with an error response and no peripheral access is

initiated on the slave bus.

Loading...

Loading...