MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

5-14 Freescale Semiconductor

The modules that are on-platform and those that are off-platform are detailed in Table 5-7.

The PBRIDGE occupies a 64 Mbyte portion of the address space. A 0.5 Mbyte portion of this space is

allocated to on-platform peripherals. The remaining 63.5 Mbytes are available for off-platform devices.

The register maps of the slave peripherals are located on 16-Kbyte boundaries. Each slave peripheral is

allocated one 16-Kbyte block of the memory map, and is activated by one of the module enables from the

PBRIDGE. Up to thirty-two 16-Kbyte external slave peripherals may be implemented, occupying

contiguous blocks of 16 Kbytes. Two global external slave module enables are available for the remaining

63 Mbytes of address space to allow for customization and expansion of addressed peripheral devices. In

addition, a single non-global module enable is also asserted whenever any of the 32 non-global module

enables is asserted.

The PBRIDGE is responsible for indicating to slave peripherals if an access is in supervisor or user mode.

The PBRIDGE may block user mode accesses to certain slave peripherals or it may allow the individual

slave peripherals to determine if user mode accesses are allowed. In addition, peripherals may be

designated as write-protected. The PBRIDGE supports the notion of trusted masters for security purposes.

Masters may be individually designated as trusted for reads, trusted for writes, or trusted for both reads

and writes, as well as being forced to look as though all accesses from a master are in user mode privilege

level.

The PBRIDGE also supports buffered writes, allowing write accesses to be terminated on the system bus

in a single clock cycle, and then subsequently performed on the slave interface. Write buffering is

controllable on a per-peripheral basis. The PBRIDGE implements a two-entry 32-bit write buffer.

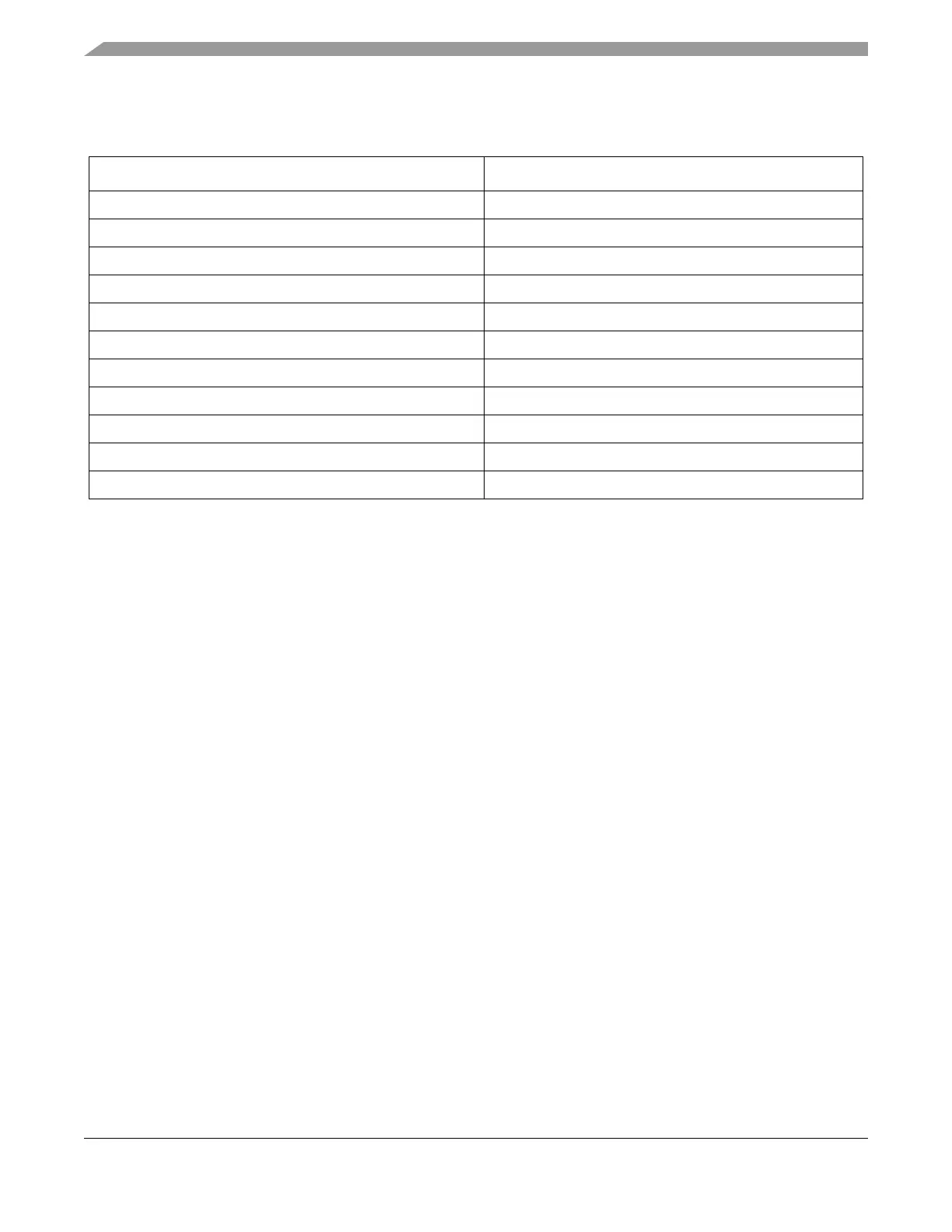

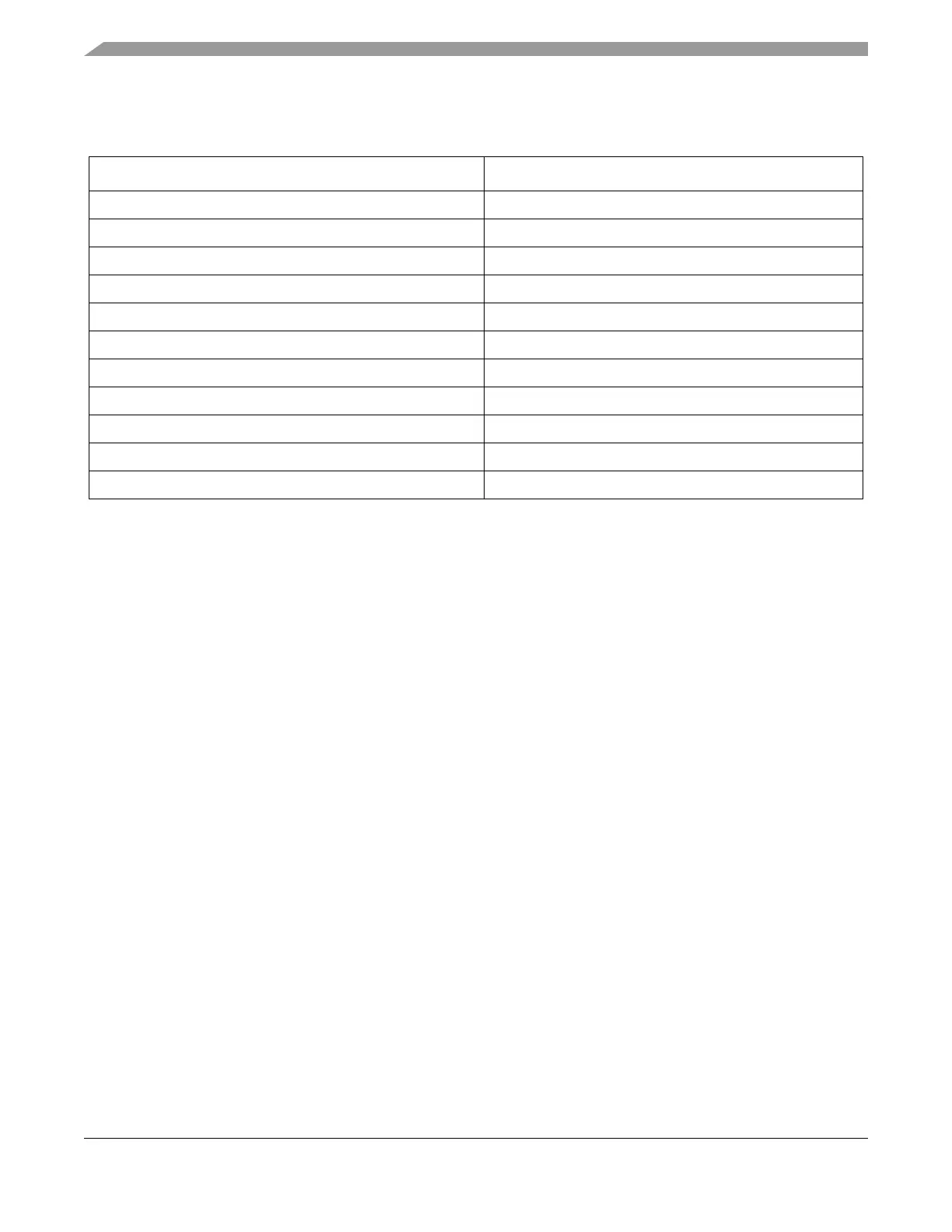

Table 5-7. On-Platform and Off-Platform Peripherals

On-Platform Off-Platform

Enhanced Direct Memory Access (eDMA) Deserial Serial Peripheral Interface (DSPI)

PBridge A and B Enhanced Queued Analog-to-Digital Converter (eQADC)

Interrupt Controller (INTC) Enhanced Serial Communication Interface (eSCI)

Error Correction Status Module (ECSM) FlexCAN Controller Area Network

Fast Ethernet Controller (FEC) Boot Assist Module (BAM)

System Bus Crossbar Switch (XBAR) System Integration Unit (SIU)

Enhanced Modular Input/Output Subsystem (eMIOS)

Frequency Modulated Phase Locked Loop (FMPLL)

Enhanced Time Processing Unit (eTPU)

External Bus Interface (EBI)

Flash Bus Interface Unit (FBIU)

Loading...

Loading...