System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

6-12 Freescale Semiconductor

6.3.1.3 System Reset Control Register (SIU_SRCR)

The SIU_SRCR enables software to generate a system or external reset. A system reset invoked by

software causes an internal reset. An external reset invoked by software asserts RSTOUT on the external

IRQ pin. When written to 1, the SER bit automatically clears.

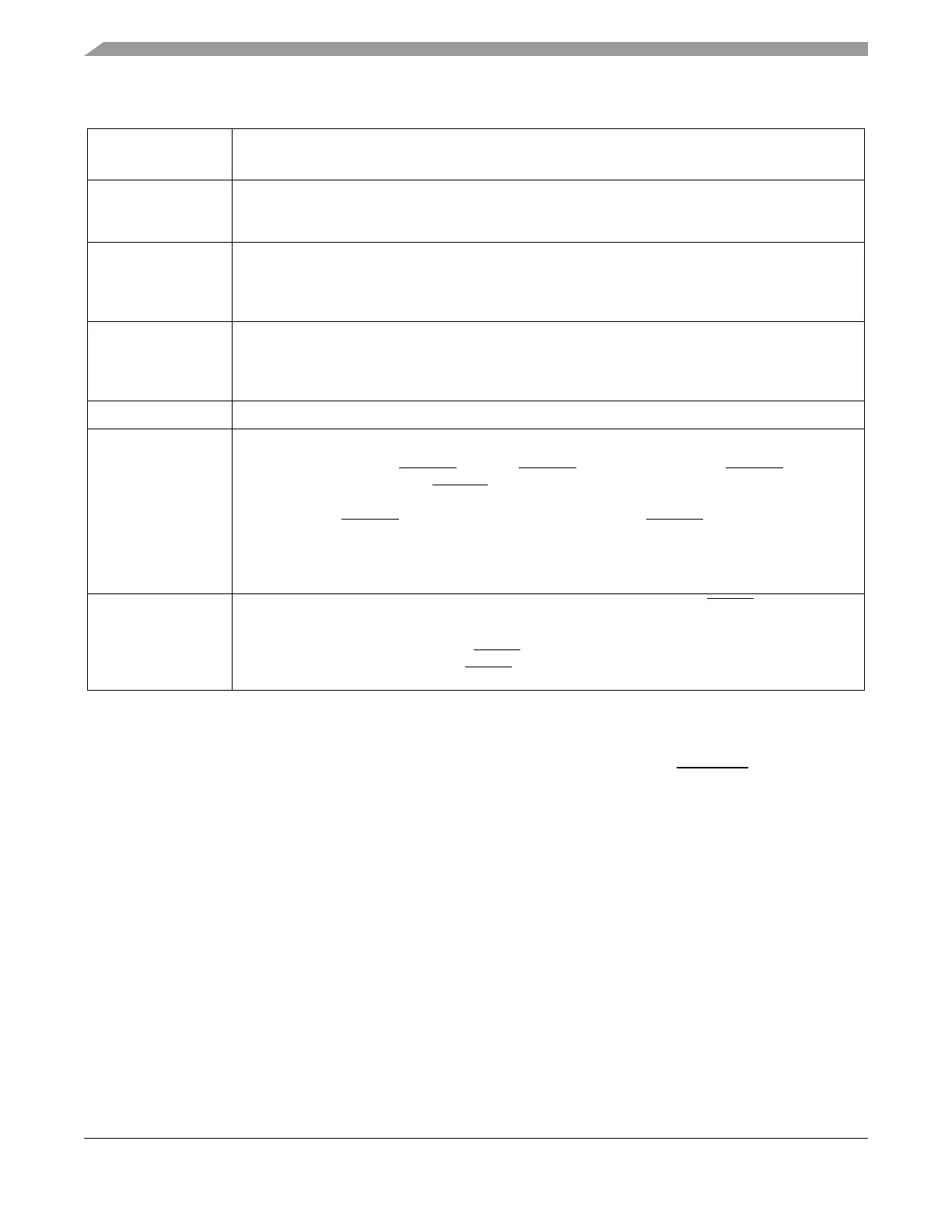

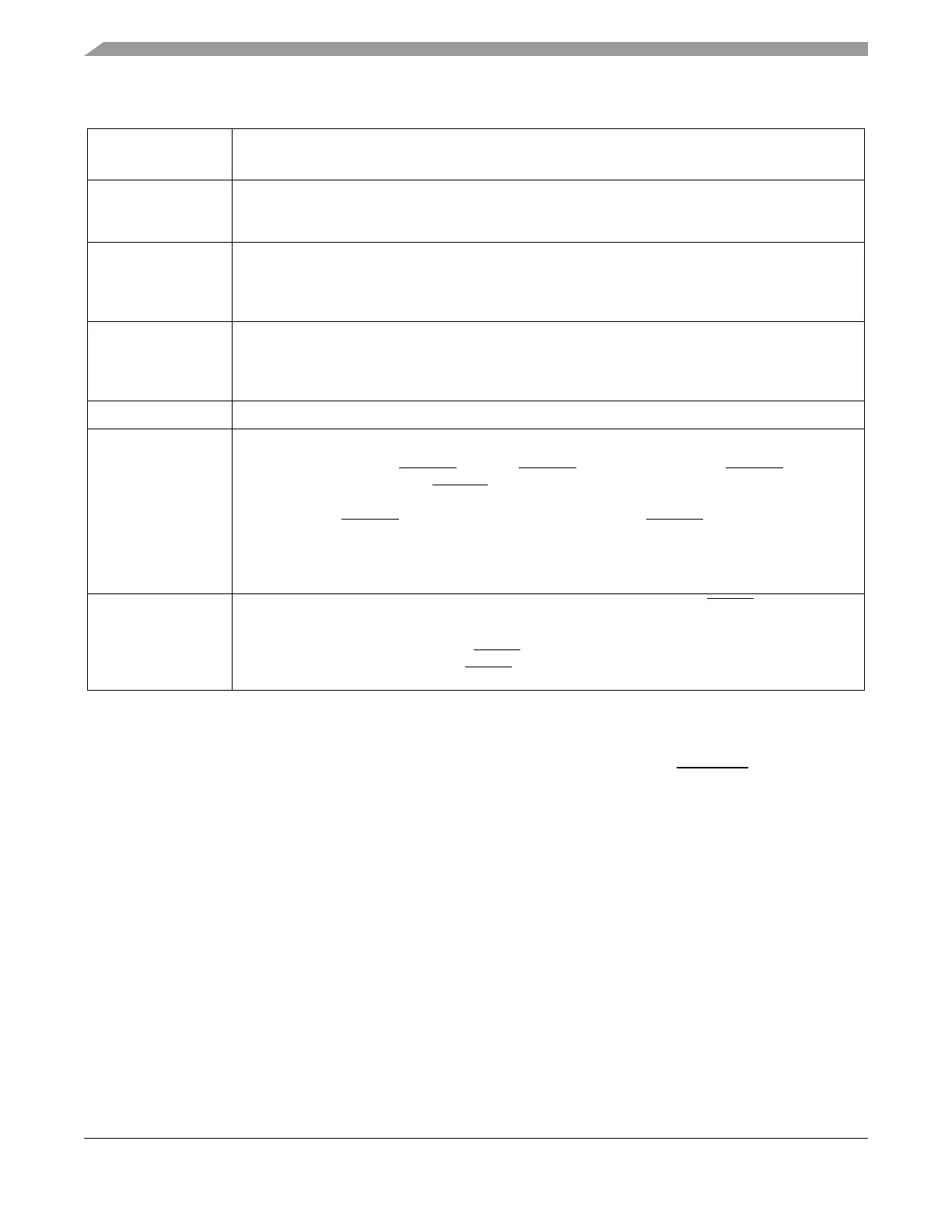

14

SSRS

Software system reset status.

0 The last reset source acknowledged by the reset controller was not a software system reset.

1 The last reset source acknowledged by the reset controller was a software system reset.

15

SERF

Software external reset flag. Read/write.

0 This bit was cleared by a write of 1, or the software external reset input to the reset controller has

not been asserted.

1 A software external reset input was asserted to the reset controller while this bit was a 0.

16

WKPCFG

Weak pull configuration pin status.

0 The WKPCFG pin latched during the last reset was a logical 0 and weak pulldown is the default

setting.

1 The WKPCFG pin latched during the last reset was a logical 1 and weak pullup is the default setting.

17–28

Reserved.

29–30

BOOTCFG

Reset configuration pin status. The BOOTCFG field is used by the BAM program to determine the

location of the reset configuration halfword. Holds the value of the BOOTCFG pins that were latched

on the last negation of the RSTOUT pin, if the RSTCFG pin was asserted. If the RSTCFG pin was not

asserted at the last negation of RSTOUT

, and the lower half or least significant halfword of the

censorship control word equals 0xFFFF or 0x0000, the BOOTCFG field is set to the value 0b10.

Otherwise, if the RSTCFG pin was negated at the last negation of RSTOUT and the lower half of the

censorship control word does not equal 0xFFFF or 0x0000, then the BOOTCFG field is set to the value

0b00. Refer to Tabl e 4- 5 for a translation of the reset configuration halfword location from the

BOOTCFG field value.

31

RGF

Reset glitch flag. Set by the reset controller when a glitch is detected on the RESET pin. This bit is

cleared by the assertion of the power-on reset input to the reset controller, or a write of 1 to the RGF

bit. Refer to Section 6.4.2.1, “RESET Pin Glitch Detect,” for more information on glitch detection.

0 No glitch has been detected on the RESET

pin.

1 A glitch has been detected on the RESET

pin.

Table 6-6. SIU_RSR Field Descriptions (Continued)

Register Bit Range

Field Name

Description

Loading...

Loading...