System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 6-11

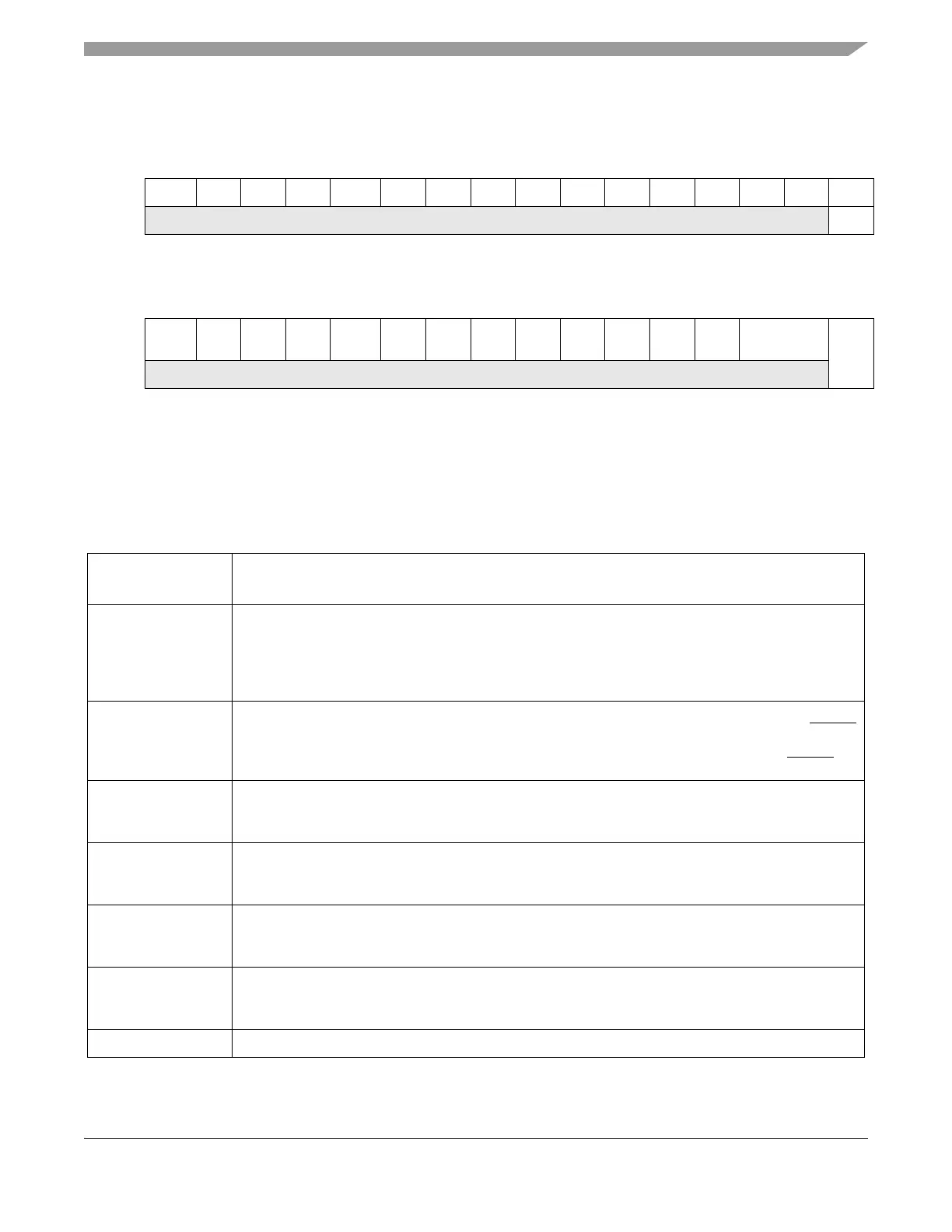

Address: Base + 0x000C Access: Read[0:5, 14:16, 29:31]/Write[15, 31]

0 123 4 56789101112131415

R

PORSERSLLRSLCRSWDRSCRS00000000SSRSSERF

W w1c

Reset

1

1 000 0 00000000000

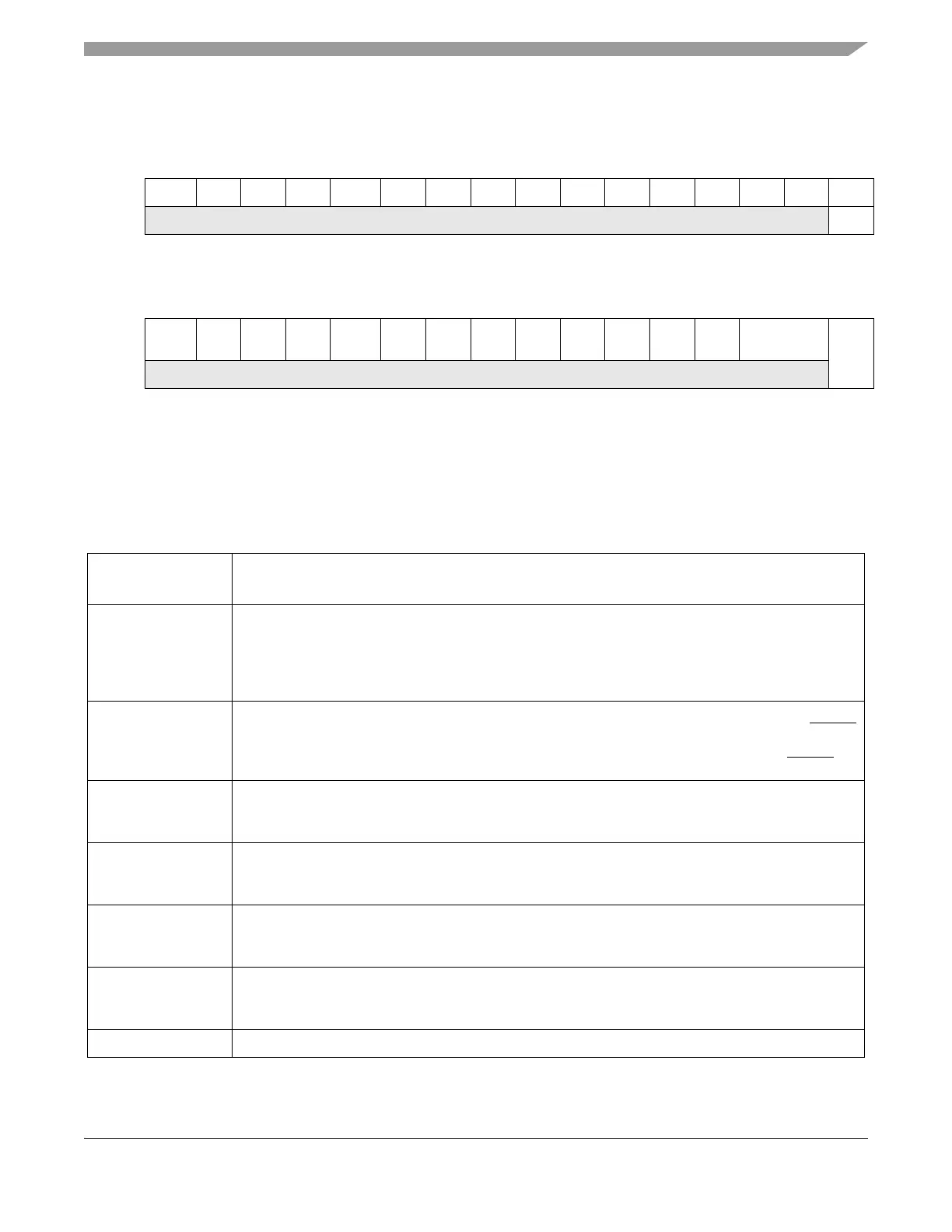

Address: Base + 0x000C Access: Read[0:5, 14:16, 29:31]/Write[15, 31]

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

WKP

CFG

2

000 0 00000000BOOTCFG

RGF

W

Reset

1

U

2

000 0 00000000 U

3

0

1

The reset status register receives its reset values during power-on reset.

2

The reset value of the WKPCFG bit is determined by the value on the WKPCFG pin at reset.

3

The reset value of the BOOTCFG field is determined by the values on the BOOTCFG[0:1] pins at reset.

Figure 6-4. Reset Status Register (SIU_RSR)

Table 6-6. SIU_RSR Field Descriptions

Register Bit Range

Field Name

Description

0

PORS

Power-on reset status.

0 Another reset source has been acknowledged by the reset controller since the last assertion of the

power-on reset input.

1 The power-on reset input to the reset controller has been asserted and no other reset source has

been acknowledged since that assertion of the power-on reset input except an external reset.

1

ERS

External reset status.

0 The last reset source acknowledged by the reset controller was not a valid assertion of the RESET

pin.

1 The last reset source acknowledged by the reset controller was a valid assertion of the RESET pin.

2

LLRS

Loss-of-lock reset status.

0 The last reset source acknowledged by the reset controller was not a loss of PLL lock reset.

1 The last reset source acknowledged by the reset controller was a loss of PLL lock reset.

3

LCRS

Loss-of-clock reset status.

0 The last reset source acknowledged by the reset controller was not a loss-of-clock reset.

1 The last reset source acknowledged by the reset controller was a loss-of-clock reset.

4

WDRS

Watchdog timer/debug reset status.

0 The last reset source acknowledged by the reset controller was not a watchdog timer or debug reset.

1 The last reset source acknowledged by the reset controller was a watchdog timer or debug reset.

5

CRS

Checkstop reset status.

0 The last reset source acknowledged by the reset controller was not an enabled checkstop reset.

1 The last reset source acknowledged by the reset controller was an enabled checkstop reset.

6–13

Reserved.

Loading...

Loading...