System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

6-14 Freescale Semiconductor

corresponding DMA/interrupt request enable bit in SIU_DIRER. The IRQ flag bit remains set until cleared

by software or through the servicing of a DMA request. The IRQ flag bits are cleared by writing a 1 to the

bits. A write of 0 has no effect.

6.3.1.5 DMA/Interrupt Request Enable Register (SIU_DIRER)

The SIU_DIRER allows the assertion of a DMA or interrupt request if the corresponding flag bit is set in

the SIU_EISR. The external interrupt request enable bits enable the interrupt or DMA request. There is

only one interrupt request from the SIU to the interrupt controller. The EIRE bits allow selection of which

external interrupt request flag bits cause assertion of the one interrupt request signal.

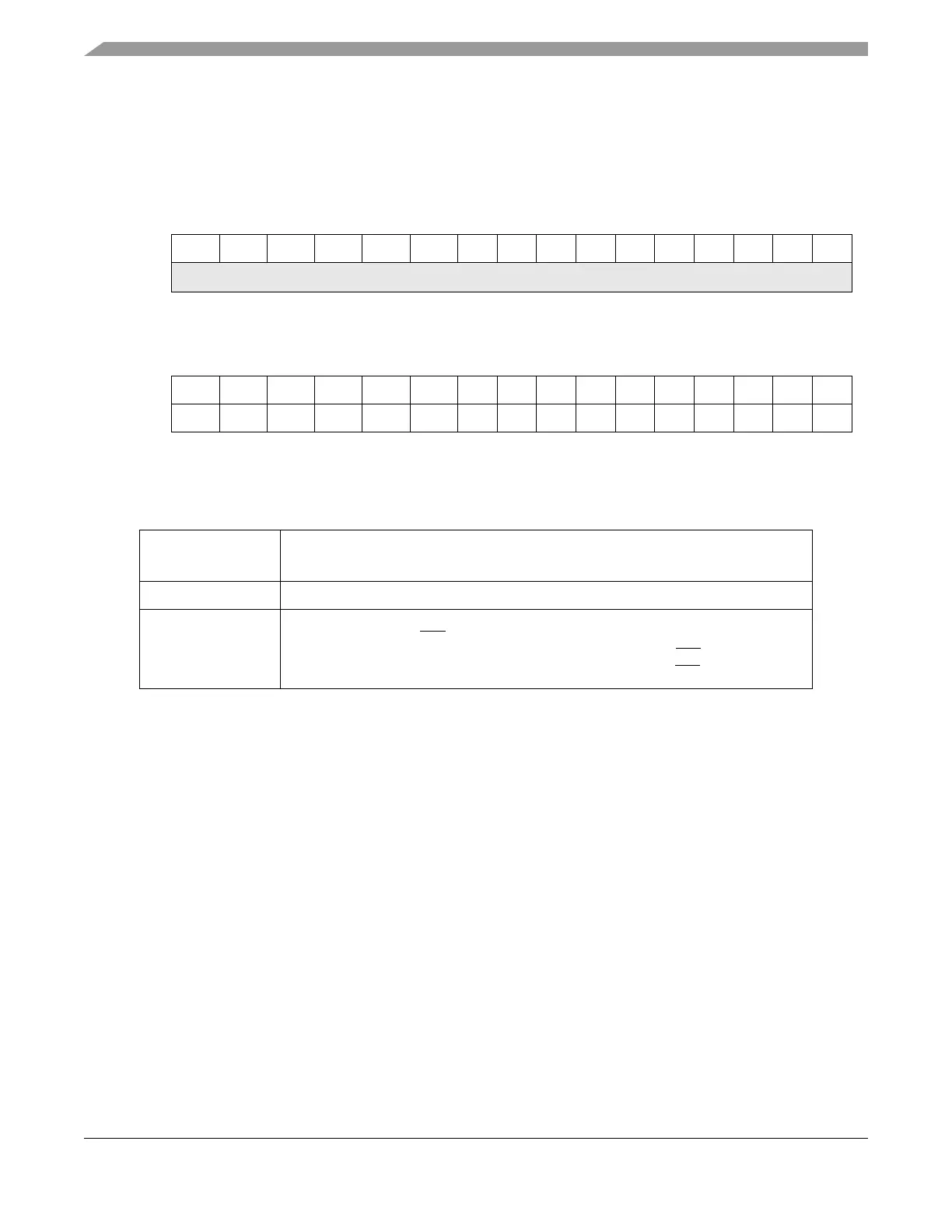

Address: Base + 0x0014 Access: Read / Write[16:31]

0123456789101112131415

R

0000000000000000

W

Reset

0000000000000000

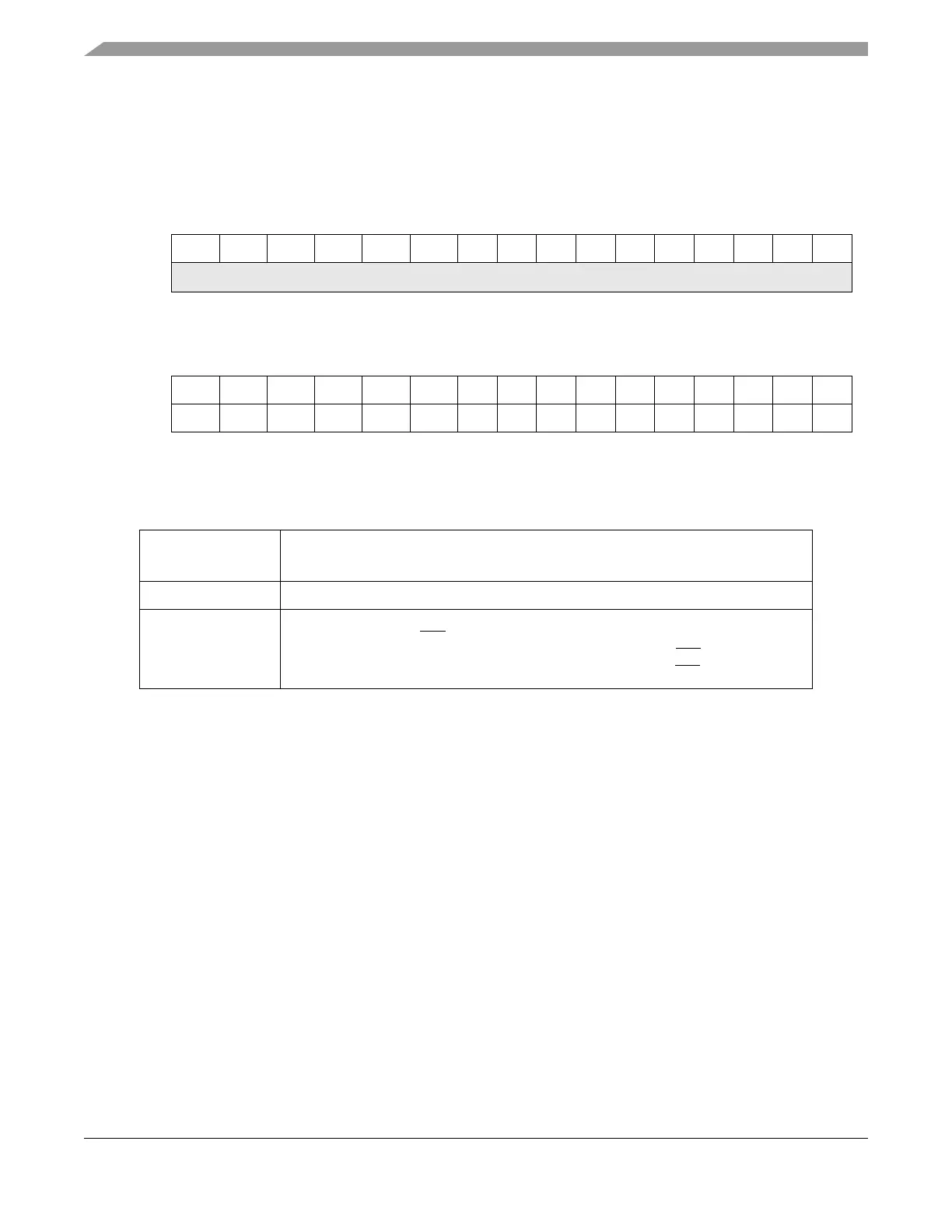

Address: Base + 0x0014 Access: Read / Write[16:31]

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

EIF15 EIF14 EIF13 EIF12 EIF11 EIF10 EIF9 EIF8 EIF7 EIF6 EIF5 EIF4 EIF3 EIF2 EIF1 EIF0

W w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset

0000000000000000

Figure 6-6. SIU External Interrupt Status Register (SIU_EISR)

Table 6-8. SIU_EISR Field Descriptions

Register Bit Range

Field Name

Function

0–15

Reserved.

16–31

EIFn

External interrupt request flag n. This bit is set when an edge-triggered event occurs

on the corresponding IRQ[n] input.

0 No edge-triggered event has occurred on the corresponding IRQ

[n] input.

1 An edge-triggered event has occurred on the corresponding IRQ[n] input.

Loading...

Loading...