System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 6-17

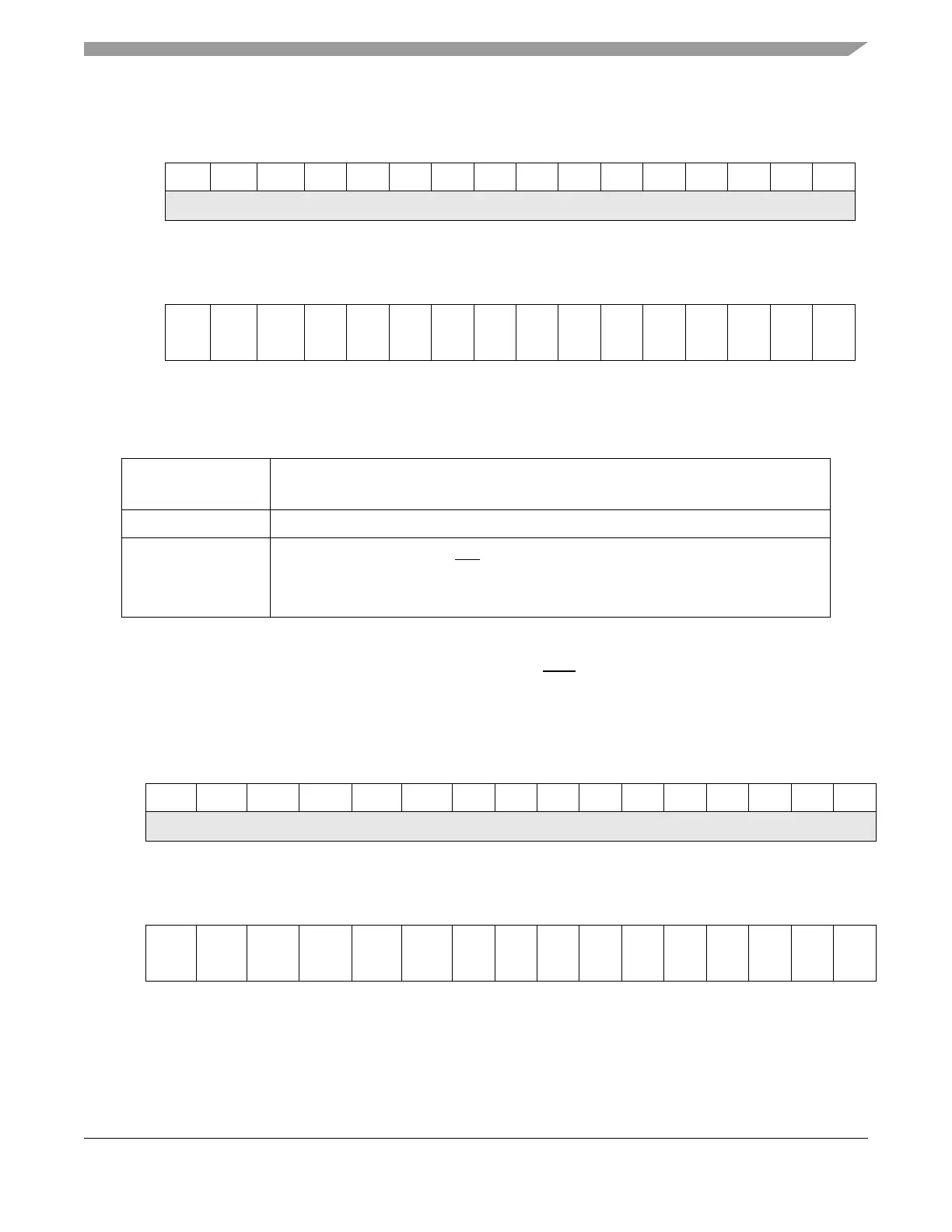

6.3.1.9 IRQ Rising-Edge Event Enable Register (SIU_IREER)

The SIU_IREER enables rising-edge triggered events for the IRQ[n] signals. Enable rising- and

falling-edge events by setting the IREE[n] bit in both the SIU_IREER and SIU_IFEER.

Address: Base + 0x0024 Access: Read/ Write[16:31]

0 1 2 3456789101112131415

R

0 0 0 0000000000000

W

Reset

0 0 0 0000000000000

Address: Base + 0x0024 Access: Read/ Write[16:31]

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

ORE15 ORE14 ORE13 ORE12 ORE11 ORE10

ORE9 ORE8 ORE7 ORE6 ORE5 ORE4 ORE3 ORE2 ORE1 ORE0

W

Reset

0 0 0 0000000000000

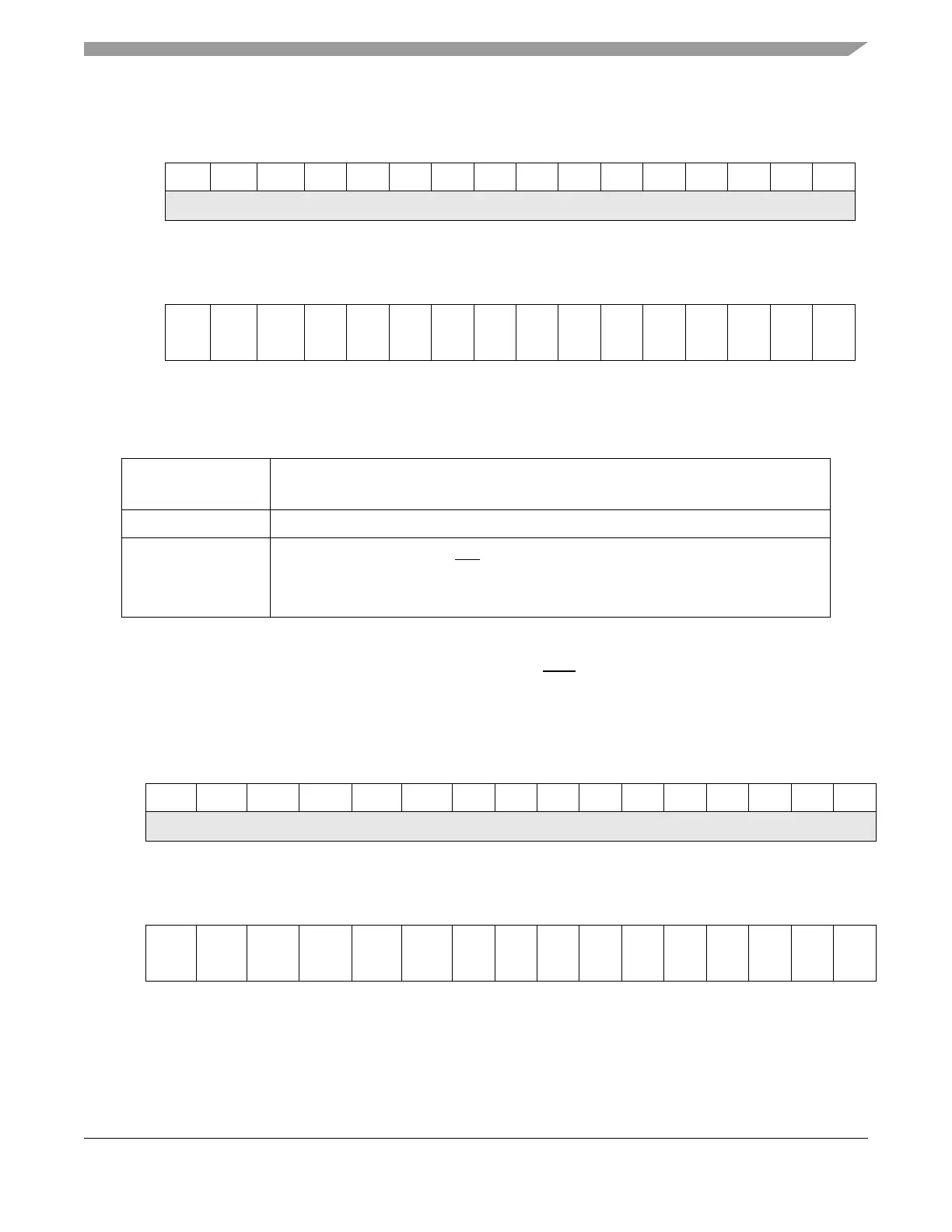

Figure 6-10. Overrun Request Enable Register (SIU_ORER)

Table 6-12. SIU_ORER Field Descriptions

Register Bit Range

Field Name

Function

0–15

Reserved.

16–31

OREn

Overrun request enable n. Enables the corresponding overrun request when an overrun

occurs on the corresponding IRQ

[n] pin.

0 Overrun request is disabled.

1 Overrun request is enabled.

Address: Base + 0x0028 Access: Read/Write [16:31]

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

0 0 0 0 0 0 0000000000

W

Reset

0 0 0 0 0 0 0000000000

Address: Base + 0x0028 Access: Read/Write [16:31]

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

IREE15 IREE14 IREE13 IREE12 IREE11 IREE10 IREE9 IREE8 IREE7 IREE6 IREE5 IREE4 IREE3 IREE2 IREE1 IREE0

W

Reset

0 0 0 0 0 0 0000000000

Figure 6-11. IRQ Rising-Edge Event Enable Register (SIU_IREER)

Loading...

Loading...