System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

6-18 Freescale Semiconductor

6.3.1.10 IRQ Falling-Edge Event Enable Register (SIU_IFEER)

The SIU_IFEER enables falling-edge triggered events on IRQ[n] pins. Enable rising- and falling-edge

events by setting bits in the SIU_IREER and SIU_IFEER registers, respectively.

6.3.1.11 IRQ Digital Filter Register (SIU_IDFR)

The SIU_IDFR specifies the amount of digital filtering on the IRQ[0]–IRQ[15] pins. The digital filter

length field specifies the number of system clocks that define the period of the digital filter and the

minimum time a signal must be held in the active state on the IRQ pins to be recognized as an edge

triggered event.

Table 6-13. SIU_IREER Field Descriptions

Register Bit Range

Field Name

Function

0–15

Reserved.

16–31

IREEn

IRQ rising-edge event enable n. Enables rising-edge triggered events on the

corresponding IRQ

[n] pin.

0 Rising-edge event is disabled.

1 Rising-edge event is enabled.

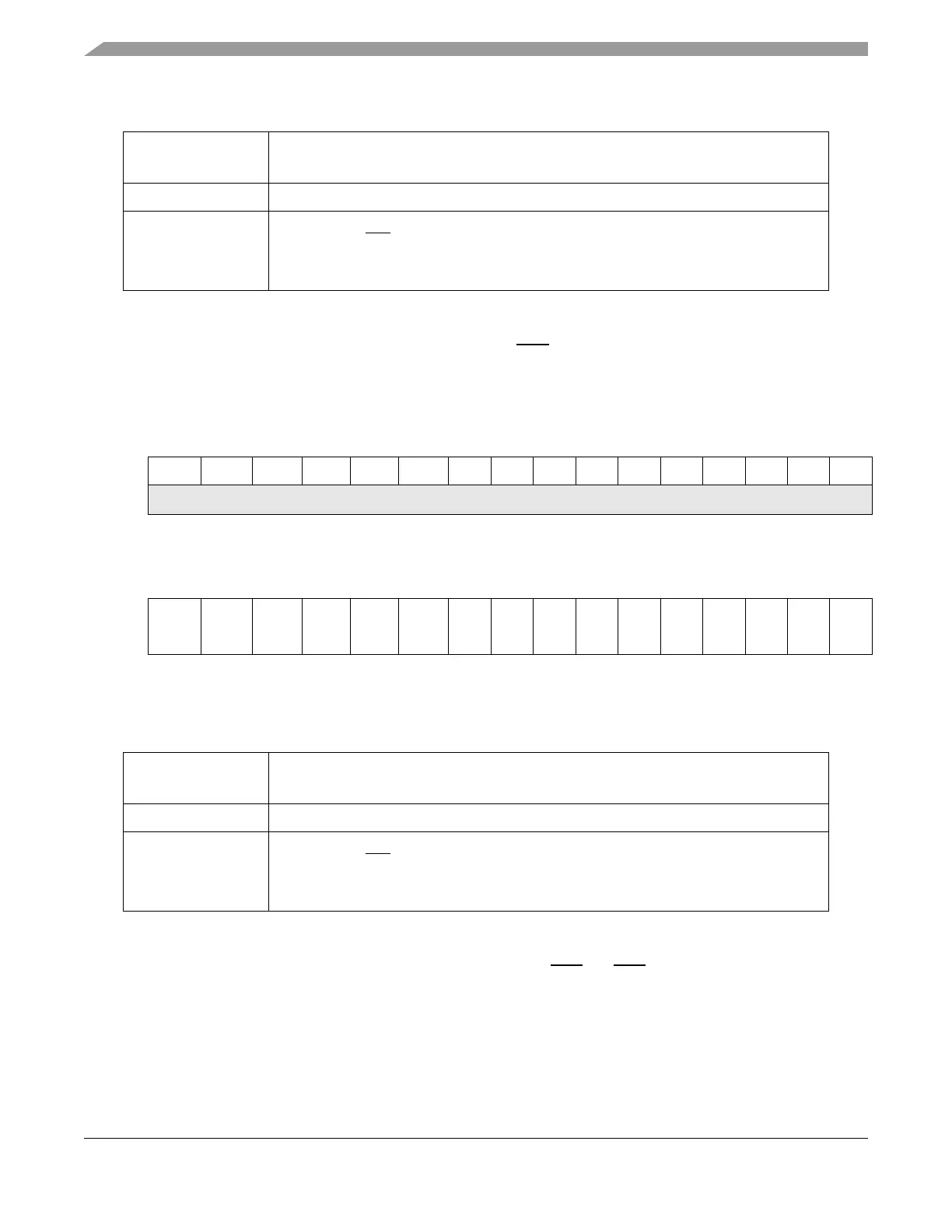

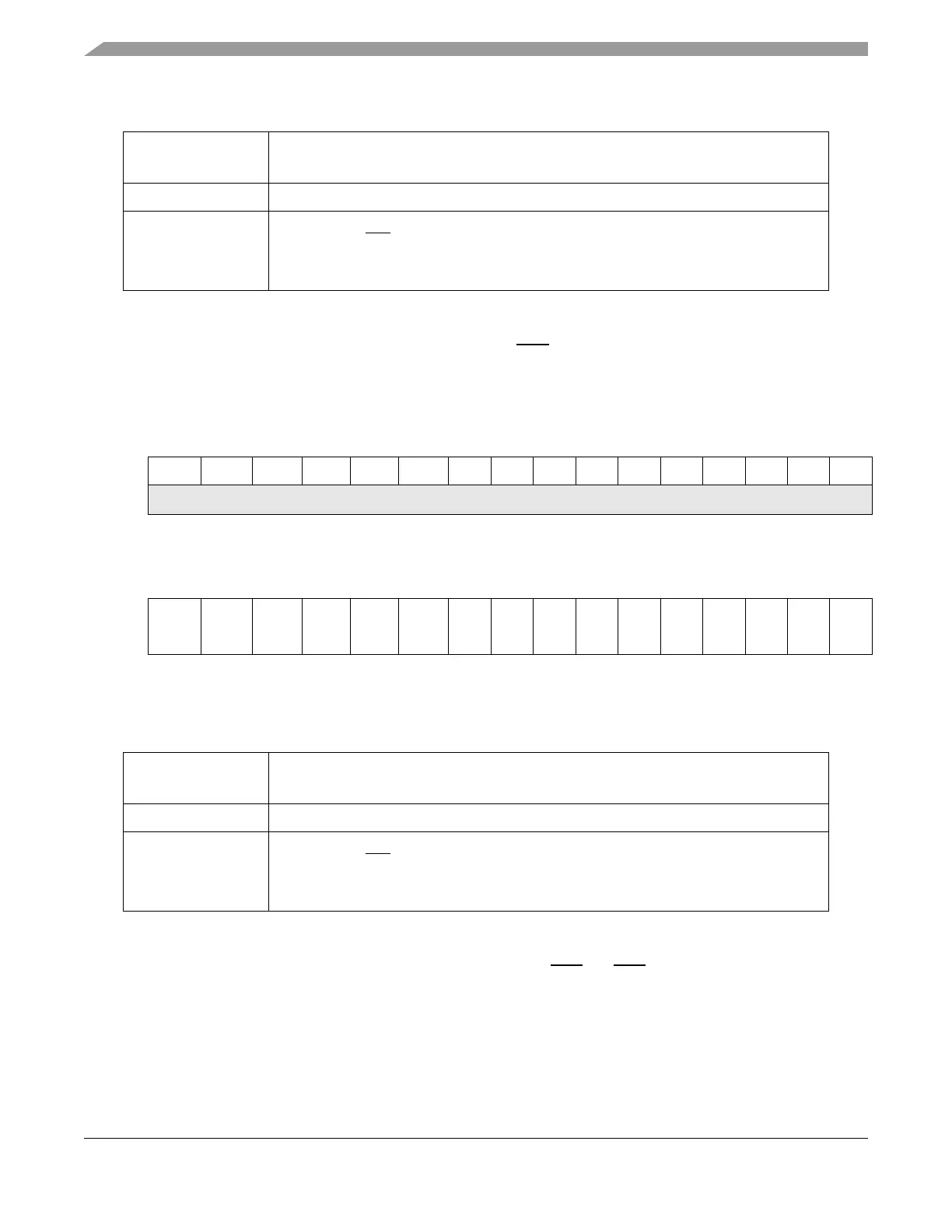

Address: Base + 0x002C Access: Read / Write[16:31]

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

0 0 0 0 0 0 0000000000

W

Reset

0 0 0 0 0 0 0000000000

Address: Base + 0x002C Access: Read / Write[16:31]

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

IFEE15 IFEE14 IREE13 IFEE12 IFEE11 IFEE10 IFEE9 IFEE8 IFEE7 IFEE6 IFEE5 IFEE4 IFEE3 IFEE2 IFEE1 IFEE0

W

Reset

0 0 0 0 0 0 0000000000

Figure 6-12. IRQ Falling-Edge Event Enable Register (SIU_IFEER)

Table 6-14. SIU_IFEER Field Descriptions

Register Bit Range

Field Name

Function

0–15

Reserved.

16–31

IFEEn

IRQ falling-edge event enable n. Enables falling-edge triggered events on the

corresponding IRQ

[n] pin.

0 Falling-edge event is disabled.

1 Falling-edge event is enabled.

Loading...

Loading...