System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

6-90 Freescale Semiconductor

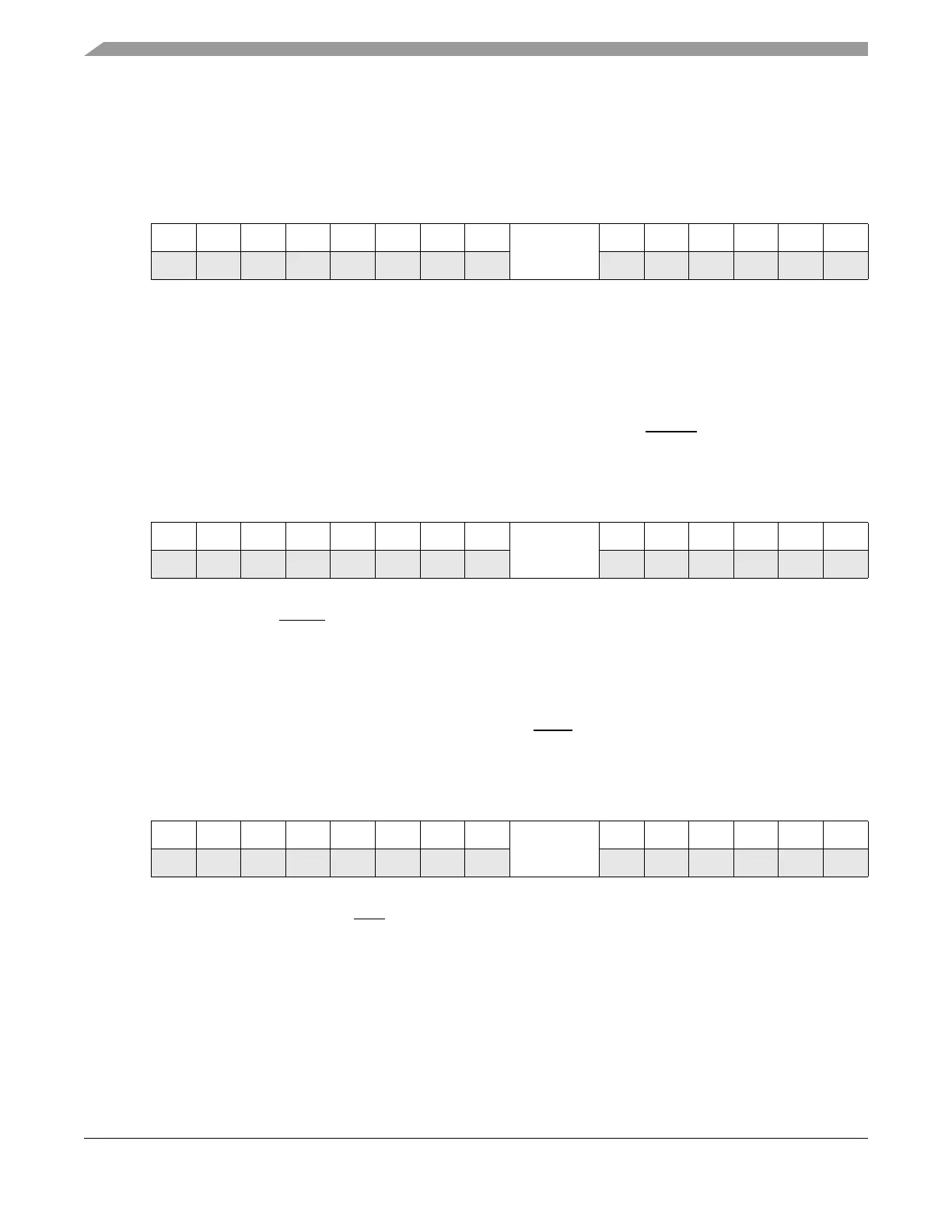

6.3.1.12.110 Pad Configuration Register 220–223 (SIU_PCR220–SIU_PCR223)

The SIU_PCR220–SIU_PCR223 registers control the drive strength of the MDO[0:3] pins.

Figure 6-122. MDO[0:3] Pad Configuration Register (SIU_PCR220–SIU_PCR223)

Refer to Table 6-16 for bit field definitions.

6.3.1.12.111 Pad Configuration Register 224–225 (SIU_PCR224–SIU_PCR225)

The SIU_PCR224–SIU_PCR225 registers control the drive strength of the MSEO[0:1] pins.

Figure 6-123. MSEO[0:1] Pad Configuration Register (SIU_PCR224–SIU_PCR225)

Refer to Table 6-16 for bit field definitions.

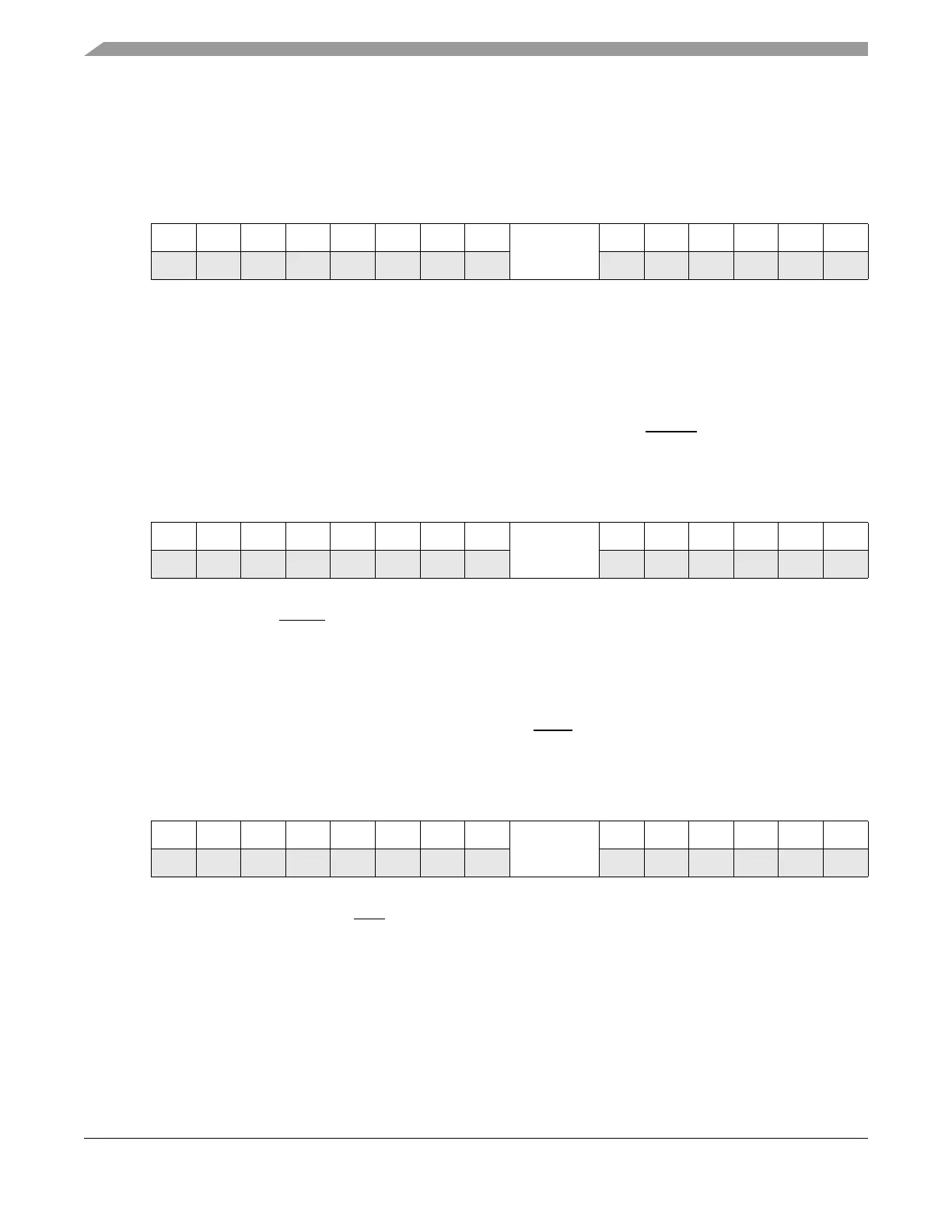

6.3.1.12.112 Pad Configuration Register 226 (SIU_PCR226)

The SIU_PCR226 register controls the drive strength of the RDY pin.

Figure 6-124. RDY Pad Configuration Register (SIU_PCR226)

Refer to Table 6-16 for bit field definitions.

Address: Base + 0x01F8 through Base + 0x01FE Access: Read / write[8:9]

0123456789101112131415

R 00000000

DSC

000000

W

RESET: 0000000011000000

Address: Base + 0x0200 and Base + 0x0202 Access: Read / write[8:9]

0123456789101112131415

R 00000000

DSC

000000

W

RESET: 0000000011000000

Address: Base + 0x0204 Access: Read / write[8:9]

0123456789101112131415

R 00000000

DSC

000000

W

RESET: 0000000011000000

Loading...

Loading...