MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

10-4 Freescale Semiconductor

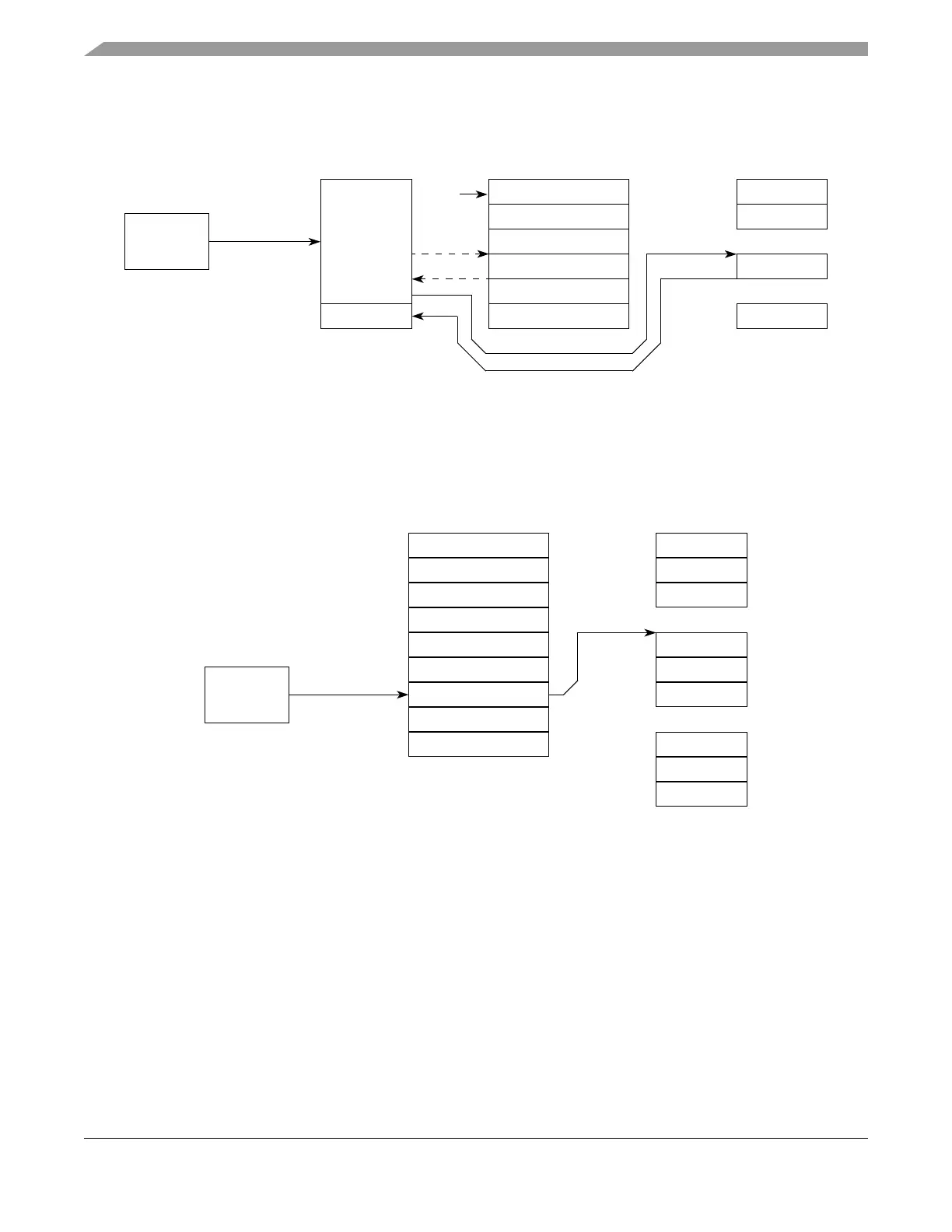

the vector of the interrupt request source. Typical program flow for software vector mode is shown in

Figure 10-4.

Figure 10-4. Program Flow—Software Vector Mode

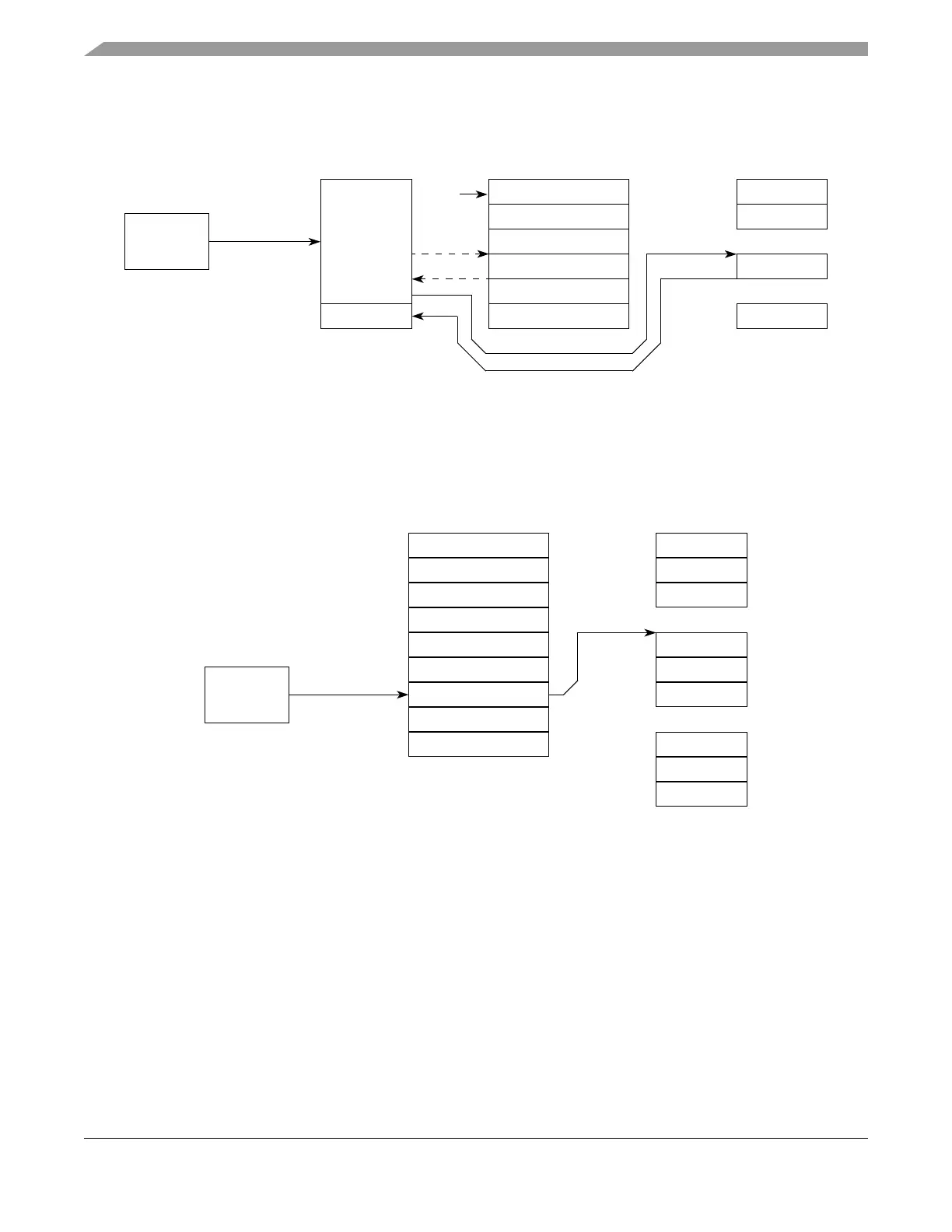

In hardware vector mode, the e200z6 branches to a unique interrupt exception handler whose location is

unique for each interrupt request source. Typical program flow for hardware vector mode is shown in

Figure 10-5.

Figure 10-5. Program Flow—Hardware Vector Mode

For high priority interrupt requests in these target applications, the time from the assertion of the interrupt

request from the peripheral to when the processor is performing useful work to service the interrupt request

needs to be minimized. The INTC may be optimized to support this goal through the hardware vector

mode, where a unique vector is provided for each interrupt request source. It also provides 16 priorities so

that lower priority ISRs do not delay the execution of higher priority ISRs. Because each individual

application will have different priorities for each source of interrupt request, the priority of each interrupt

request is configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC

supports the priority ceiling protocol for coherent accesses. By providing a modifiable priority mask, the

ISR

NOTES:

1 The number of interrupt sources in the

ISR_0 address ISR_0

ISRISR_1

•

•

•

ISR

ISR_n

•

•

•

ISR

ISR_3071

ISR_n address

ISR_307 address

ISR_1 address

•

•

•

•

•

•

Prolog

(Including

Using IACKR

to get Vector

then bl ISR_n

Epilog

IVPR + IVOR4

IRQn

Take n

IACKR

InstructionsAddressInstructionsAddress

MPC5553 is 210, which includes 13 reserved.

VTBA

Prologb handler_0 handler_0

ISR

•

•

•

•

•

•

ISR

•

•

•

•

•

•

Instructions

NOTE:

‘b ISR_n’ is technically part of the handler.

Epilog

Prolog

Epilog

ISR

Prolog

Epilog

handler_n

handler_307

b handler_1

•

•

•

b handler_2

•

•

•

b handler_n

b handler_307

IVPR + 0x00

IVPR + 0x10

IVPR + 0x20

IVPR + n[0x10]

IVPR + 0x1330

IRQn

Take n

Address

Loading...

Loading...