MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

10-14 Freescale Semiconductor

10.3.1.5 INTC Software Set/Clear Interrupt Registers

(INTC_SSCIR0 – INTC_SSCIR7)

The INTC_SSCIRn support the setting or clearing of software settable interrupt requests. These registers

contain eight independent sets of bits to set and clear a corresponding flag bit by software. With the

exception of being set by software, this flag bit behaves the same as a flag bit set within a peripheral. This

flag bit generates an interrupt request within the INTC just like a peripheral interrupt request. Writing a 1

to SETn will leave SETn unchanged at 0 but will set CLRn. Writing a 0 to SETn will have no effect. CLRn

is the flag bit. Writing a 1 to CLRn will clear it. Writing a 0 to CLRn will have no effect. If a 1 is written

to a pair SETn and CLRn bits at the same time, CLRn will be asserted, regardless of whether CLRn was

asserted before the write.

Although INTC_SSCIn is 8 bits wide, it can be accessed with a single 16-bit or 32-bit access, provided

that the access does not cross a 32-bit boundary.

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

Reg Addr Base + 0x0018

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0000000000000000

W

Reset0000000000000000

Reg Addr Base + 0x0018

Figure 10-11. INTC End-of-Interrupt Register (INTC_EOIR)

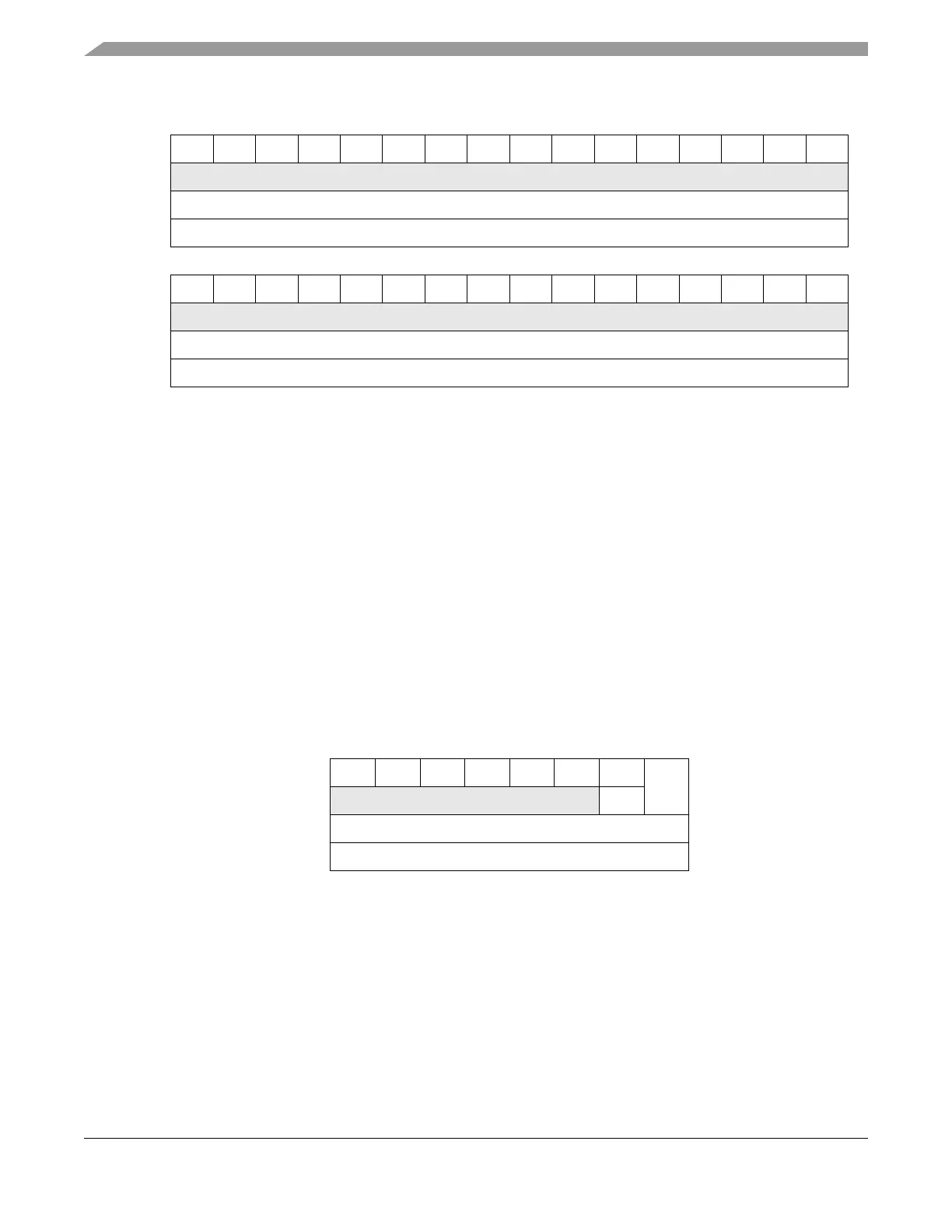

01234567

R0000000CLRn

W SETn

Reset00000000

Reg Addr Base + 0x0020 + n

Figure 10-12. INTC Software Set/Clear Interrupt Register 0–7

(INTC_SSCIR0–INTC_SSCIR7)

Loading...

Loading...