MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 10-15

10.3.1.6 INTC Priority Select Registers (INTC_PSR0 – INTC_PSR307)

The INTC_PSRn support the selection of an individual priority for each source of interrupt request. The

unique vector of each peripheral or software settable interrupt request determines which INTC_PSRn is

assigned to that interrupt request. The software settable interrupt requests 0–7 are assigned vectors 0–7,

and their priorities are configured in INTC_PSR0–INTC_PSR7, respectively. The peripheral interrupt

requests are assigned vectors 8–307 (MPC5554)/8–211 (MPC5553) and their priorities are configured in

INTC_PSR8 through INTC_PSR307 (MPC5554) / INTC_PSR8 through INTC_PSR211 (MPC5553),

respectively.

Although INTC_PSRn is 8 bits wide, it can be accessed with a single 16-bit or 32-bit access, provided that

the access does not cross a 32-bit boundary.

NOTE

The PRIn field of an INTC_PSRn must not be modified while its

corresponding peripheral or software settable interrupt request is asserted.

Table 10-7. INTC_SSCIR0–INTC_SSCIR7 Field Descriptions

Bits Name Description

0–5 — Reserved.

6SETn Set flag bits. Writing a 1 will set the corresponding CLRn bit. Writing a 0 will have no effect.

Each SETn always will be read as a 0.

7CLRn Clear flag bits. CLRn is the flag bit. Writing a 1 to CLRn will clear it provided that a 1 is not

written simultaneously to its corresponding SETn bit. Writing a 0 to CLRn will have no

effect.

0 Interrupt request not pending within INTC.

1 Interrupt request pending within INTC.

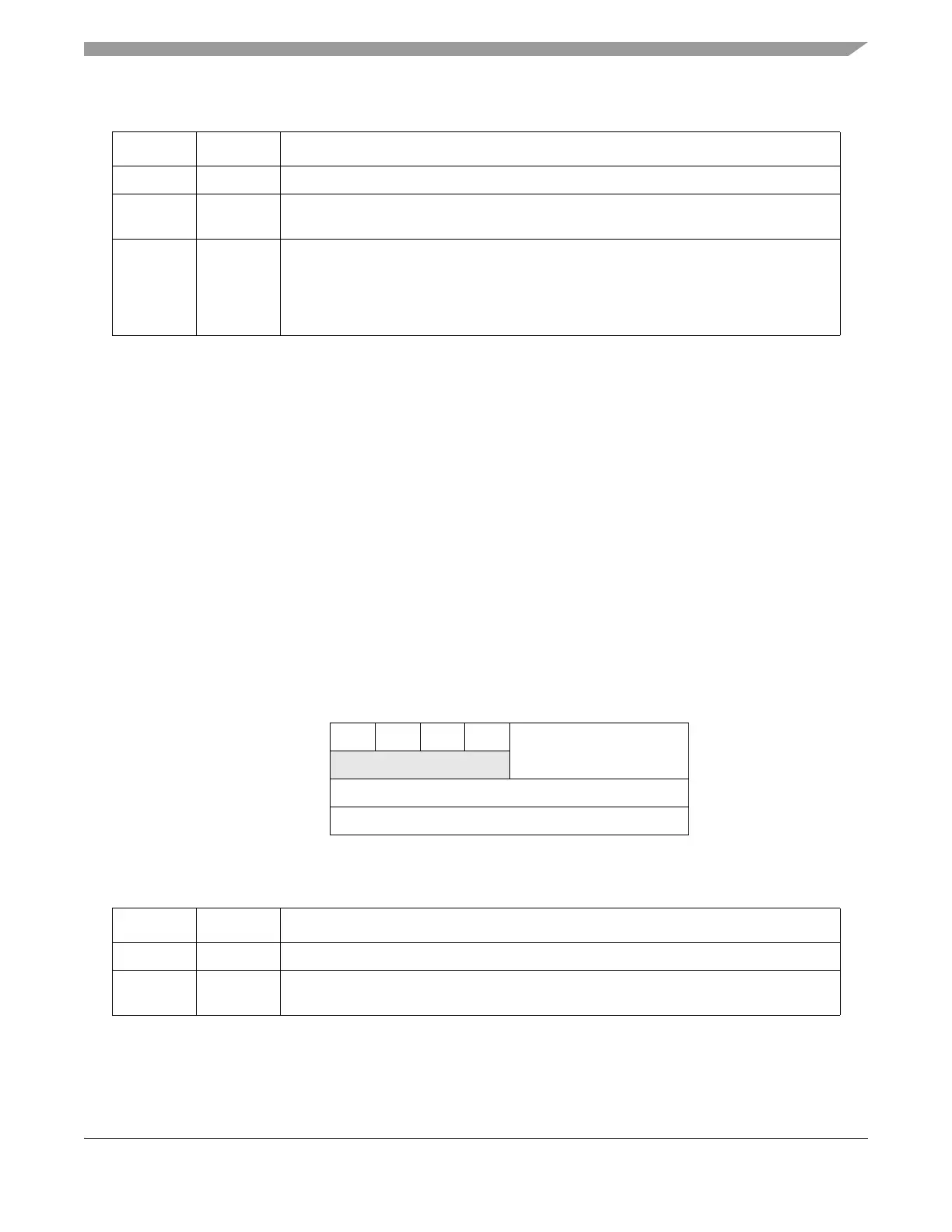

01234567

R0000 PRIn

W

Reset00000000

Reg Addr Base + 0x0040 + n

Figure 10-13. INTC Priority Select Register (INTC_PSR0–INTC_PSR307)

Table 10-8. INTC_PSR0–INTC_PSR307 Field Descriptions

Bits Name Description

0–3 — Reserved.

4–7 PRIn Priority select. Selects the priority for the interrupt requests. Refer to the field values in

Ta bl e 1 0- 5.

Loading...

Loading...