MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 11-13

NOTE

To ensure proper operation across all MPC5500 MCUs, execute an mbar or

msync instruction between the write to change the FMPLL_SYNCR[MFD]

and the read to check the lock status shown by FMPLL_SYNSR[LOCK].

Furthermore, buffering writes to the FMPLL, as controlled by

PBRIDGE_A_OPACR[BW0], must be disabled.

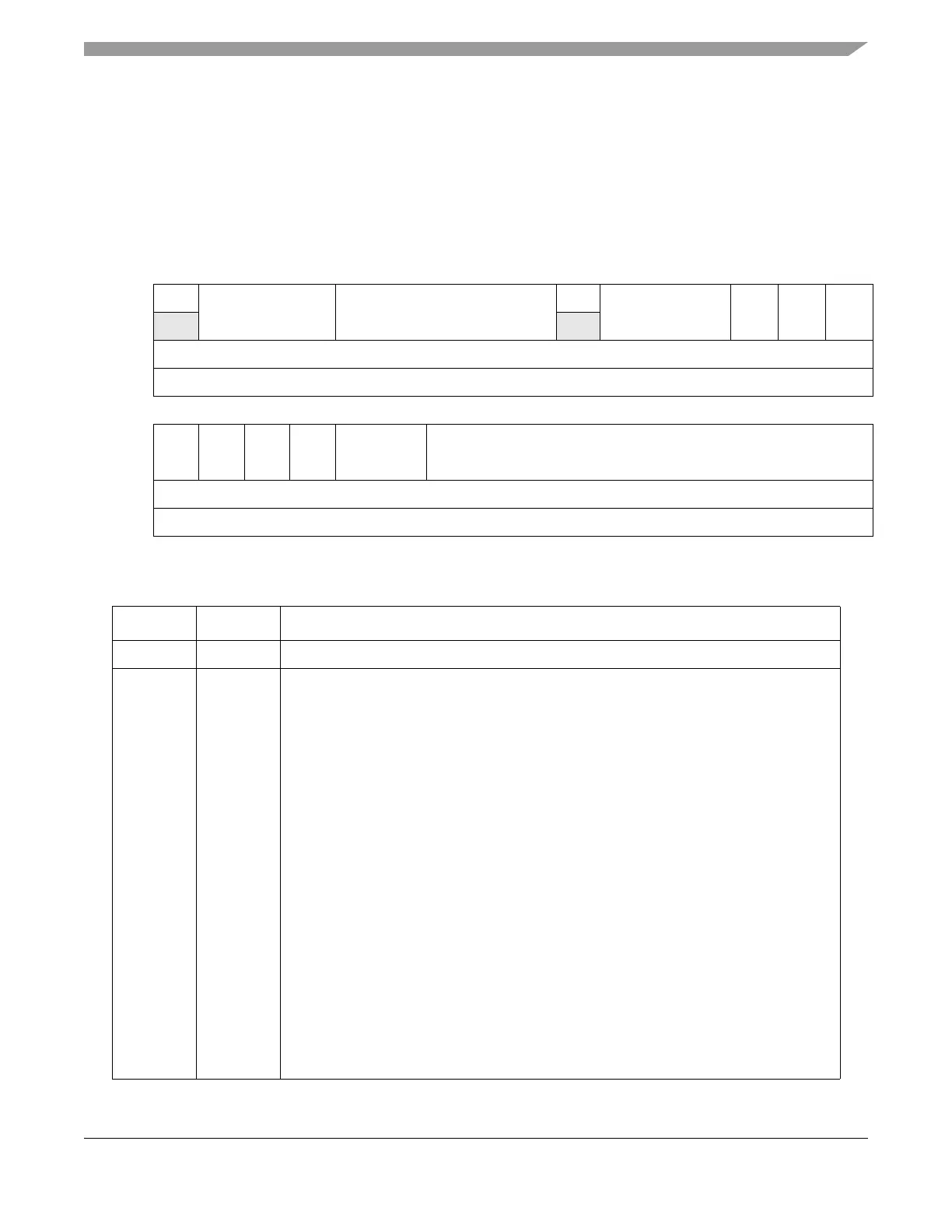

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R 0 PREDIV MFD 0 RFD LOC

EN

LOL

RE

LOC

RE

W

Reset00000001000100 0 0

Reg Addr Base + 0x0000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RDIS

CLK

LOL

IRQ

LOC

IRQ

RATE DEPTH EXP

W

Reset00000000000000 0 0

Reg Addr Base + 0x0000

Figure 11-8. Synthesizer Control Register (FMPLL_SYNCR)

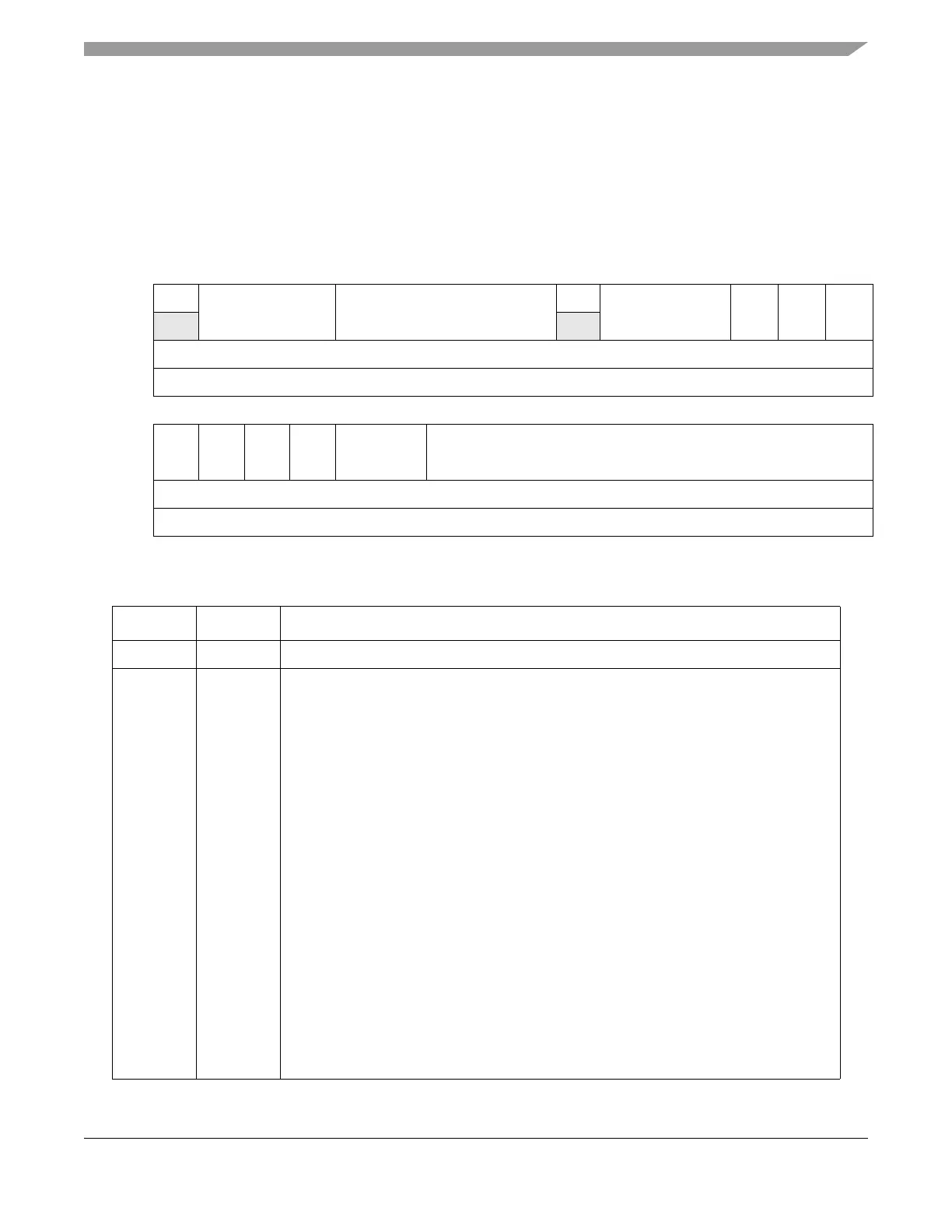

Table 11-5. FMPLL_SYNCR Field Descriptions

Bits Name Description

0 — Reserved.

1–3 PREDIV

[0:2]

The PREDIV bits control the value of the divider on the input clock. The output of the

pre-divider circuit generates the reference clock (F

prediv

) to the FMPLL analog loop. When

the PREDIV bits are changed, the FMPLL will immediately lose lock. To prevent an

immediate reset, the LOLRE bit must be cleared before writing the PREDIV bits. In 1:1

(dual-controller) mode, the PREDIV bits are ignored and the input clock is fed directly to

the analog loop.

000 Divide by 1

001 Divide by 2

010 Divide by 3

011 Divide by 4

100 Divide by 5

101–111Reserved

Note: Programming a PREDIV value such that the ICO operates outside its specified

range will cause unpredictable results and the FMPLL will not lock. Refer to the MPC5553

Microcontroller Data Sheet and MPC5554 Microcontroller Data Sheet for details on the

ICO range.

Note: To avoid unintentional interrupt requests, disable LOLIRQ before changing PREDIV

and then reenable it after acquiring lock.

Note: When using crystal reference mode or external reference mode, The PREDIV value

must not be set to any value that causes the phase/frequency detector to go below 4 MHz.

That is, the crystal (F

ref_crystal

) or external clock (F

ref_ext

) frequency divided by the PREDIV

value creates the F

prediv

frequency that must be greater than or equal to 4 MHz – 20 MHz.

Refer to the device Data Sheet for F

prediv

values.

Loading...

Loading...