MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 11-19

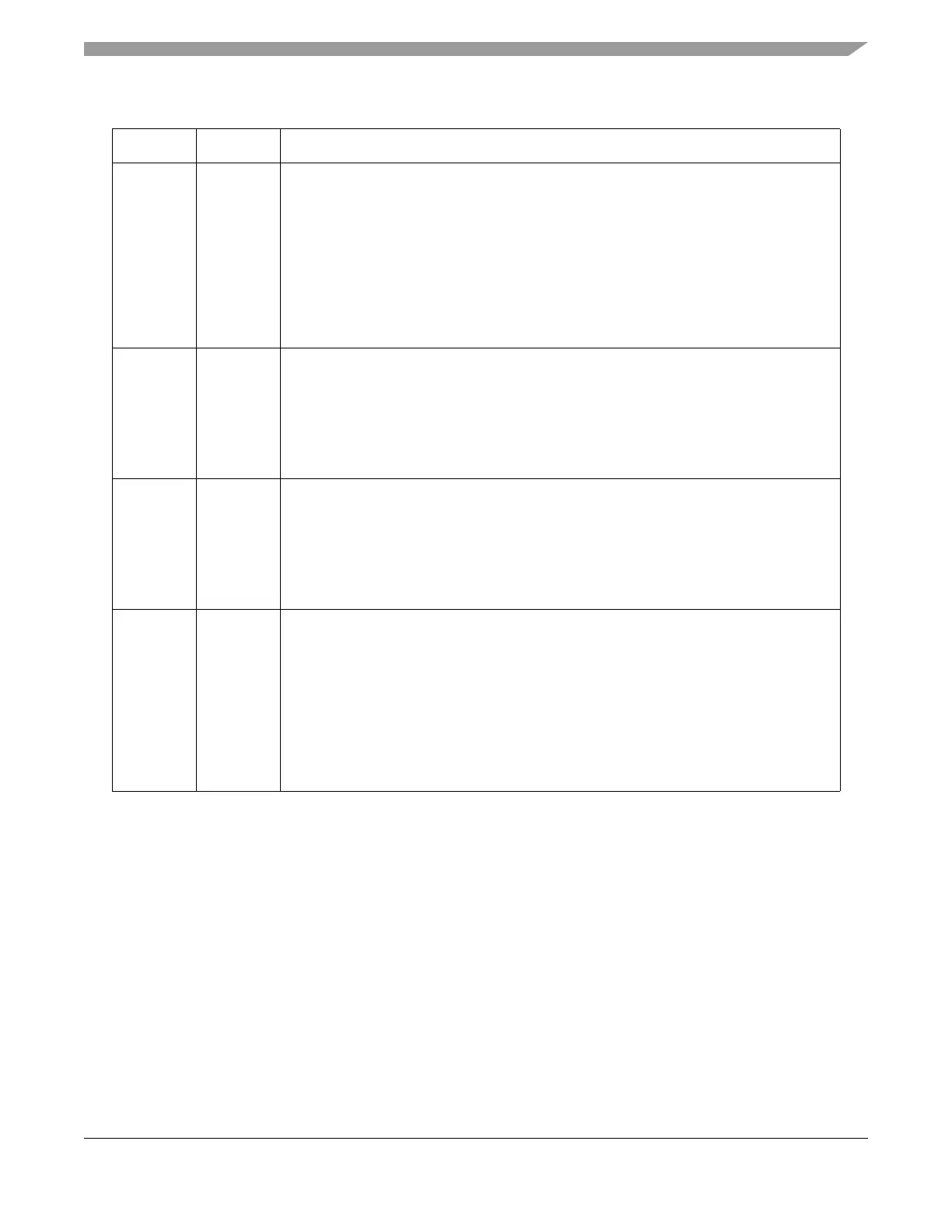

28 LOCK

PLL lock status bit. Indicates whether the FMPLL has acquired lock. If the LOCK bit is read

when the FMPLL simultaneously loses lock or acquires lock, the bit does not reflect the

current condition of the FMPLL.

If operating in bypass mode, LOCK remains cleared after reset. Refer to the frequency as

defined in the MPC5553 Microcontroller Datasheet and MPC5554 Microcontroller

Datasheet for the lock/unlock range.

0 PLL is unlocked.

1 PLL is locked.

29 LOCF Loss-of-clock flag. This bit provides the interrupt request flag. This is a write 1 to clear

(w1c) bit; to clear the flag, the user must write a 1 to the bit. Writing 0 has no effect.

Asserting reset will clear the flag. This flag is sticky in the sense that if clocks return to

normal after the flag has been set, the bit will remain set until cleared by either writing 1 or

asserting reset.

0 Interrupt service not requested

1 Interrupt service requested

30 CALDONE Calibration complete. Indicates whether the calibration sequence has been completed

since the last time modulation was enabled. If CALDONE = 0 then the calibration

sequence is either in progress or modulation is disabled. If CALDONE = 1 then the

calibration sequence has been completed, and frequency modulation is operating.

0 Calibration not complete.

1 Calibration complete.

Note: FM relocking does not start until calibration is complete.

31 CALPASS Calibration passed. Indicates whether the calibration routine was successful. If

CALPASS = 1 and CALDONE = 1 then the routine was successful. If CALPASS = 0 and

CALDONE = 1, then the routine was unsuccessful. When the calibration routine is initiated

the CALPASS is asserted. CALPASS remains asserted until either modulation is disabled

by clearing the DEPTH bits in the FMPLL_SYNCR or a failure occurs within the FMPLL

calibration sequence.

0 Calibration unsuccessful.

1 Calibration successful.

If calibration is unsuccessful, then actual depth is not guaranteed to match the desired

depth.

Table 11-6. FMPLL_SYNSR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...