MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

11-18 Freescale Semiconductor

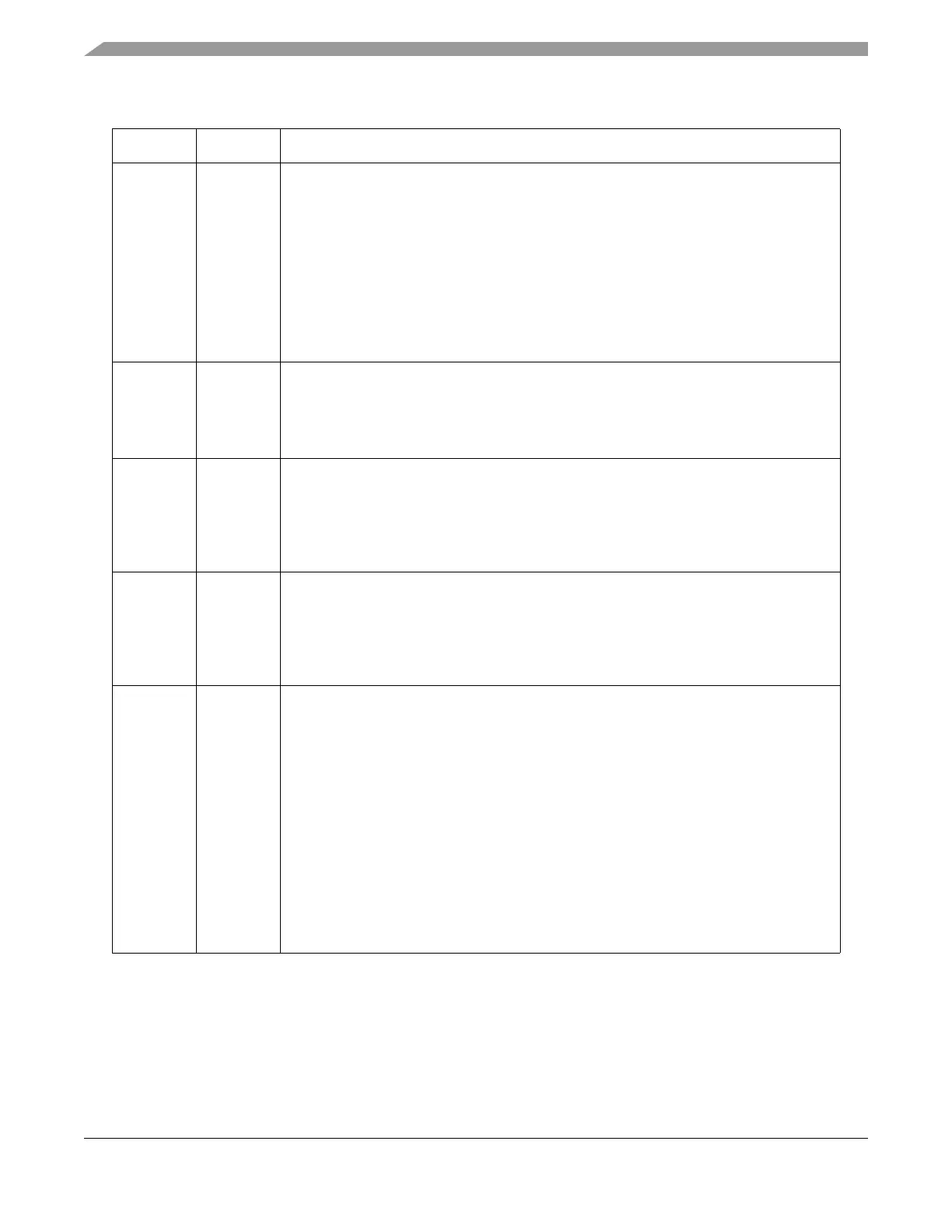

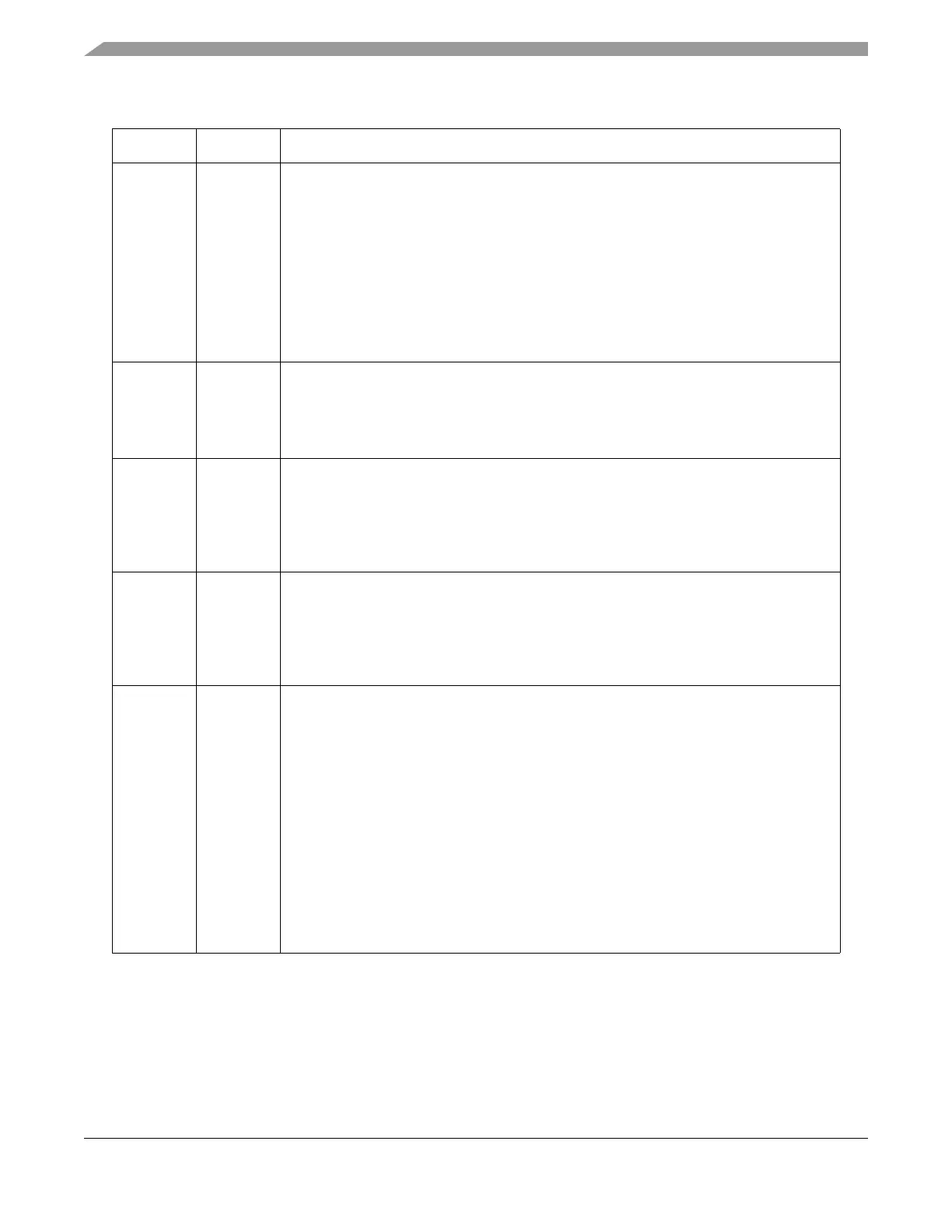

23 LOC Loss-of-clock status. Indicates whether a loss-of-clock condition is present when operating

in crystal reference, external reference, or dual-controller mode, If LOC = 0, the system

clocks are operating normally. If LOC = 1, the system clocks have failed due to a reference

failure or a FMPLL failure. If the read of the LOC bit and the loss-of-clock condition occur

simultaneously, the bit does not reflect the current loss of clock condition. If a loss-of-clock

condition occurs which sets this bit and the clocks later return to normal, this bit will be

cleared.

A loss of clock condition can only be detected if LOCEN = 1. LOC is always 0 in bypass

mode.

0 Clocks are operating normally

1 Clocks are not operating normally.

24 MODE Clock mode. Determined at reset, this bit indicates which clock mode the system is

utilizing. See Chapter 4, “Reset,” for details on how to configure the system clock mode

during reset.

0 PLL bypass mode.

1 PLL clock mode.

25 PLLSEL PLL mode select. Determined at reset, this bit indicates in which mode the FMPLL

operates. This bit is cleared in dual-controller and bypass mode. See Chapter 4, “Reset,”

for details on how to configure the system clock mode during reset. See Ta ble 1 1- 1 for

more information.

0 Dual-controller mode.

1 Crystal reference or external reference mode.

26 PLLREF PLL clock reference source. Determined at reset, this bit indicates whether the PLL

reference source is an external clock or a crystal reference. This bit is cleared in dual

controller mode and bypass mode. See Chapter 4, “Reset,” for details on how to configure

the system clock mode during reset.

0 External clock reference chosen.

1 Crystal clock reference chosen.

27 LOCKS Sticky FMPLL lock status bit. A sticky indication of FMPLL lock status. LOCKS is set by the

lock detect circuitry when the FMPLL acquires lock after one of the following:

• a system reset

• a write to the FMPLL_SYNCR which modifies the MFD and PREDIV bits

• the enabling of frequency modulation

Whenever the FMPLL loses lock, LOCKS is cleared. LOCKS remains cleared even after

the FMPLL relocks, until one of the three previously-stated conditions occurs.

Furthermore, if the LOCKS bit is read when the FMPLL simultaneously loses lock, the bit

does not reflect the current loss of lock condition.

If operating in bypass mode, LOCKS remains cleared after reset. In crystal reference,

external reference, and dual-controller mode, LOCKS is set after reset.

0 PLL has lost lock since last system reset, a write to FMPLL_SYNCR to modify the MFD

and PREDIV bit fields, or frequency modulation enabled.

1 PLL has not lost lock since last system reset, a write to FMPLL_SYNCR to modify the

MFD and PREDIV bit fields, or frequency modulation enabled.

Table 11-6. FMPLL_SYNSR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...